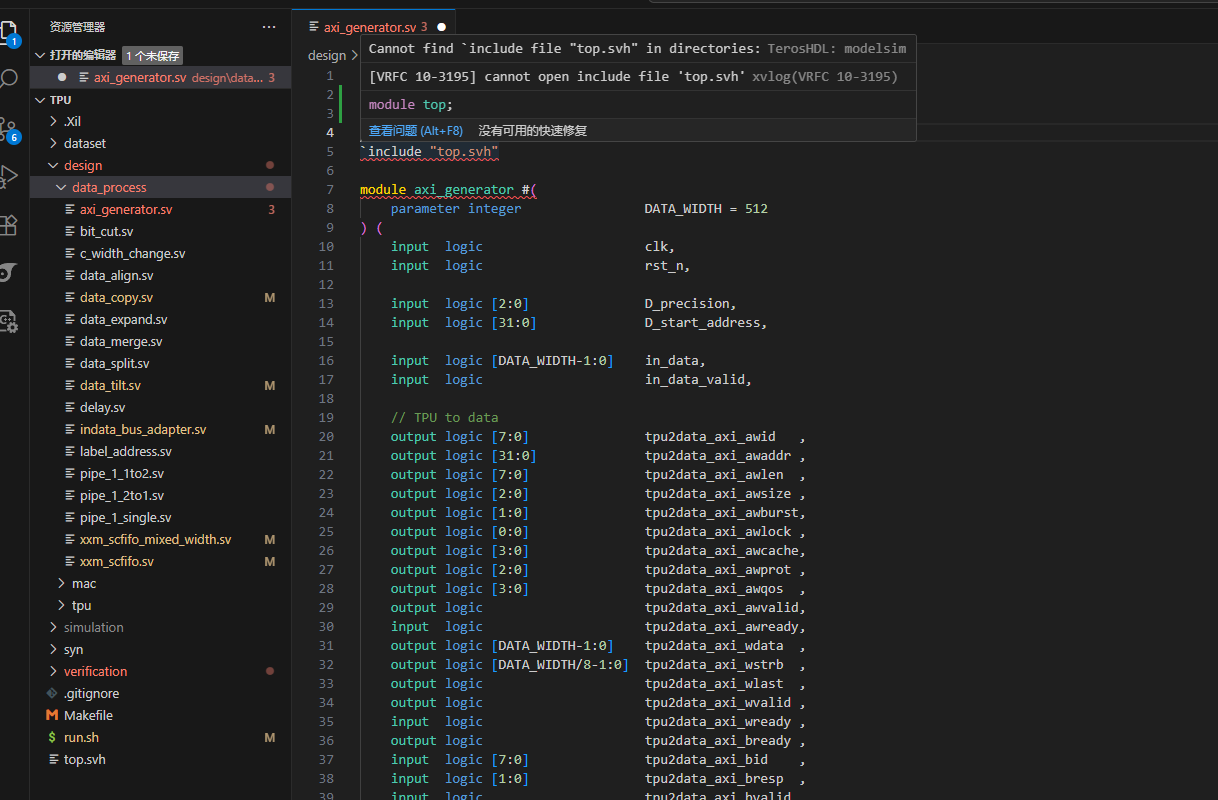

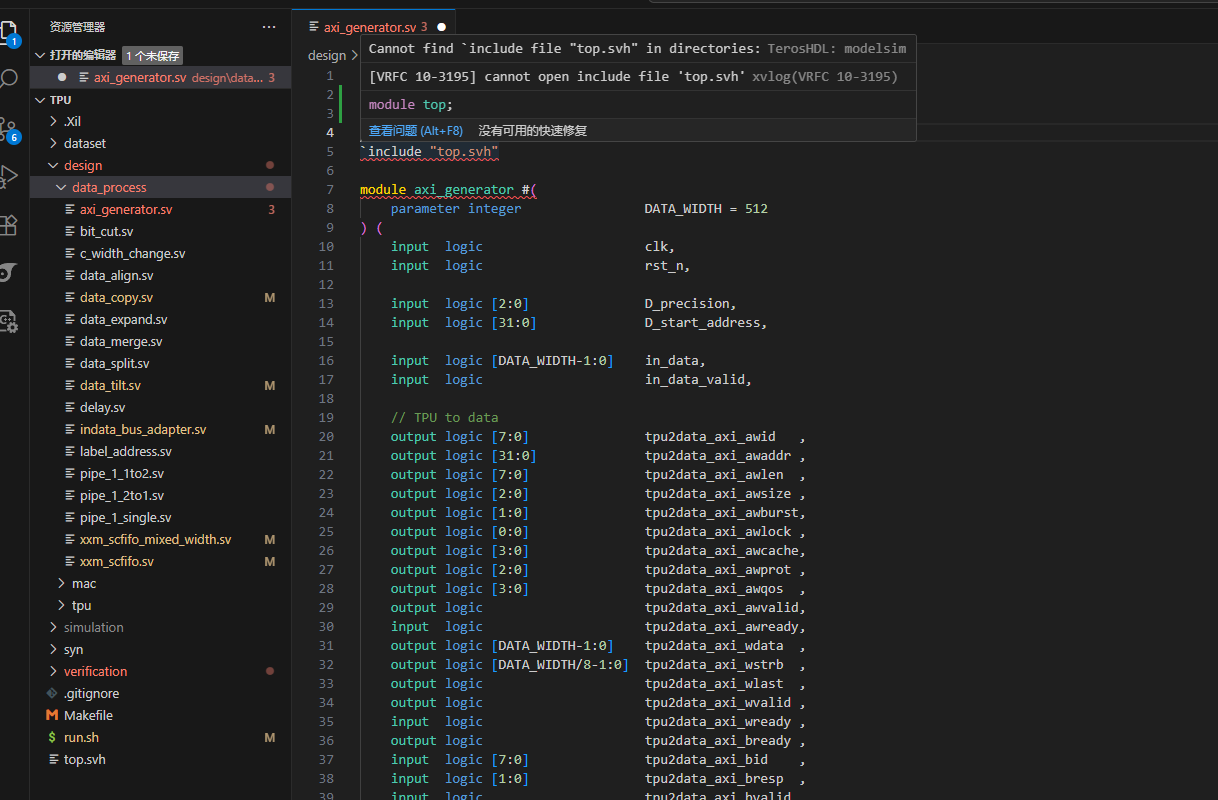

使用vscode编写verilog代码时,出现如下问题

`include引用.svh文件错误,无法找到include的文件,我把引用改为绝对路径也不行

使用vscode编写verilog代码时,出现如下问题

晚上好🌙🌙🌙

本答案参考通义千问

在使用 VSCode 编写 Verilog 代码时,如果遇到 include 引用 .svh 文件报错 的问题,通常是由于 文件路径不正确 或 语言服务器未识别头文件路径 导致的。以下是详细的解决方案:

检查文件名和扩展名

确保 .svh 文件的实际名称与 include 命令中的一致(包括大小写和扩展名)。

`include "my_header.svh"

如果文件是 my_header.svh,但你写成 my_header.vh,就会出错。

检查相对路径是否正确

VSCode 中默认使用的是 相对于当前文件的路径。例如:

src/top_module.vincludes/my_header.svh正确的 include 应为:

`include "includes/my_header.svh"

尝试使用绝对路径

如果相对路径不起作用,可以尝试使用绝对路径,但需注意:

示例:

`include "/home/user/project/includes/my_header.svh"

⚠️ 注意:不同操作系统(Windows / Linux / macOS)的路径格式不同,要确保路径符合当前系统。

如果你使用的是 VLS(Verilog Language Server),它可能无法自动识别头文件路径。你可以通过以下方式配置:

安装 VLS 插件

如果还没有安装,可以在 VSCode 中搜索并安装 "Verilog Language Server" 扩展。

创建 vls.json 配置文件

在项目根目录下创建一个 vls.json 文件,并添加头文件路径:

{

"searchPaths": [

"./includes",

"./rtl",

"./testbench"

]

}

这会告诉 VLS 在这些目录中查找头文件。

重启 VSCode

修改配置后,重启 VSCode 以使更改生效。

如果你希望更灵活地管理路径,可以使用宏定义来设置头文件路径:

`define INCLUDE_PATH "includes/"

`include `INCLUDE_PATH`my_header.svh

这样可以通过修改宏定义来统一管理路径,避免硬编码。

.svh 文件有读取权限。.svh 文件使用的是 UTF-8 编码,否则可能会导致解析错误。假设你的文件结构如下:

project/

├── src/

│ └── top_module.v

└── includes/

└── my_header.svh

top_module.v 内容:`include "includes/my_header.svh"

module top_module (

input clk,

output reg [7:0] data

);

// 使用头文件中的定义

`ifdef MY_DEFINE

assign data = 8'hAA;

`endif

endmodule

includes/my_header.svh 内容:`define MY_DEFINE

| 错误信息 | 可能原因 | 解决方案 |

|----------|----------|----------|

| No such file or directory | 路径错误或文件不存在 | 检查文件名、路径、大小写 |

| Invalid include path | 使用了 < 而不是 " " | 改为双引号 |

| Header not found | 语言服务器未识别路径 | 配置 vls.json 或 settings.json |

在 VSCode 的 settings.json 中添加以下内容,可以帮助提升 Verilog 编辑体验:

{

"verilog.includePath": [

"${workspaceFolder}/includes",

"${workspaceFolder}/rtl"

],

"verilog.linting.enable": true,

"verilog.linting.tool": "verilator"

}

include 报错的步骤define 宏定义路径 提高灵活性。如你提供具体的错误信息或文件结构,我可以进一步帮助你定位问题。