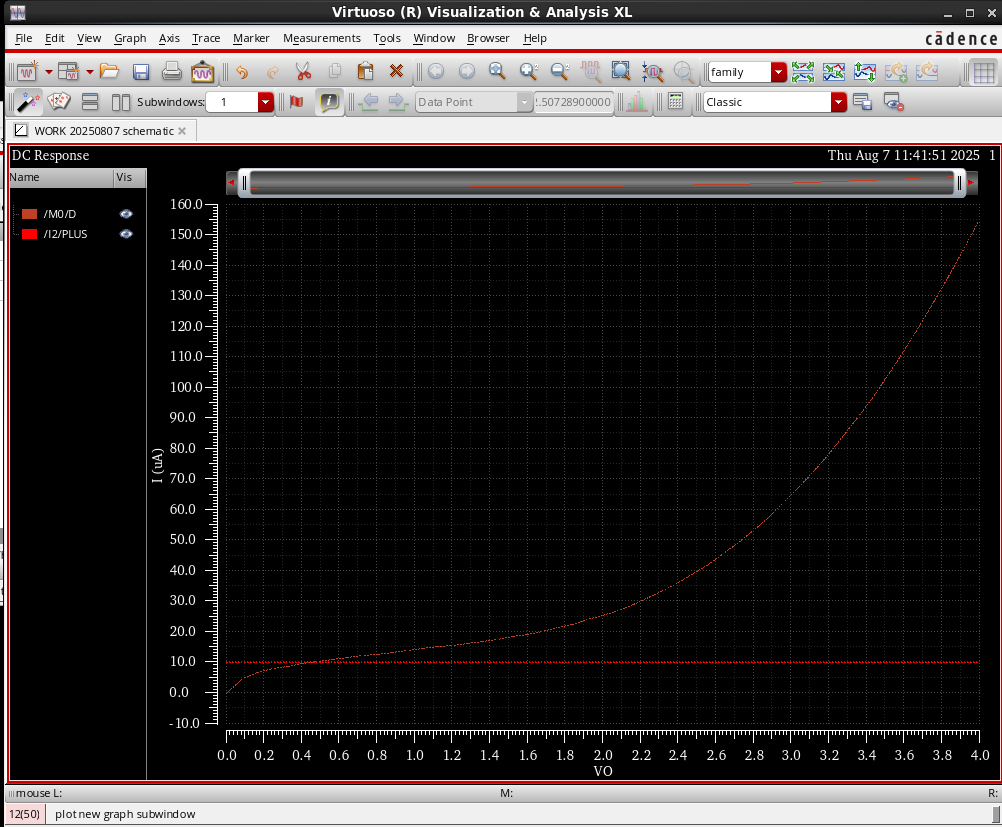

问题:输出曲线应该在进入饱和区后大致等于10uA,但是看输出曲线是一直上升的,不知道怎么解释,deepseek说是异常的,哪怕被击穿也不会到达160uA,想问下输出曲线正不正常。

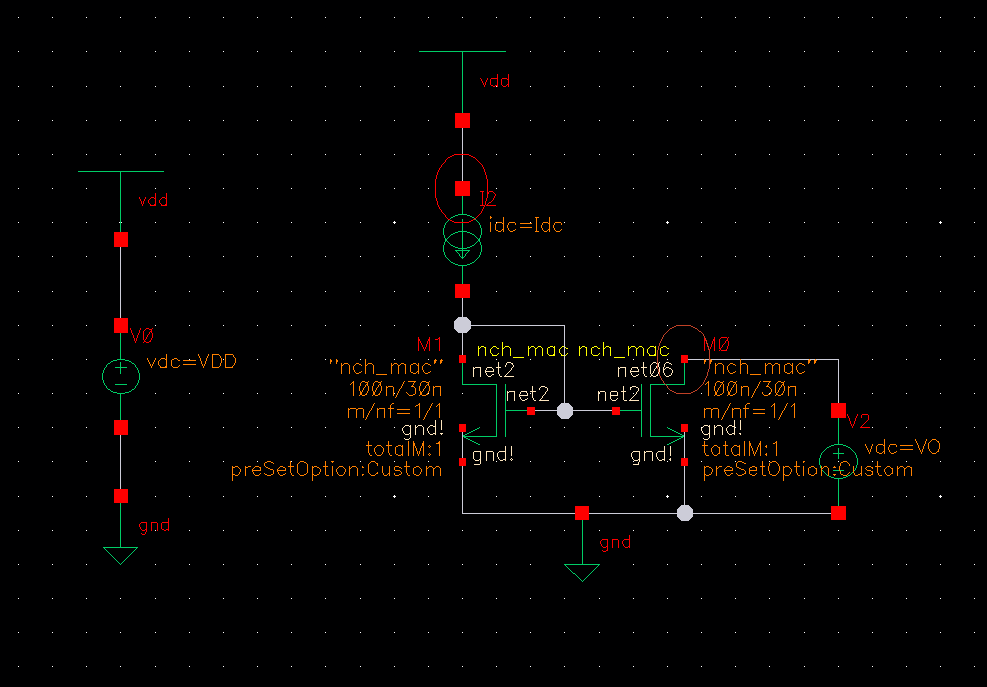

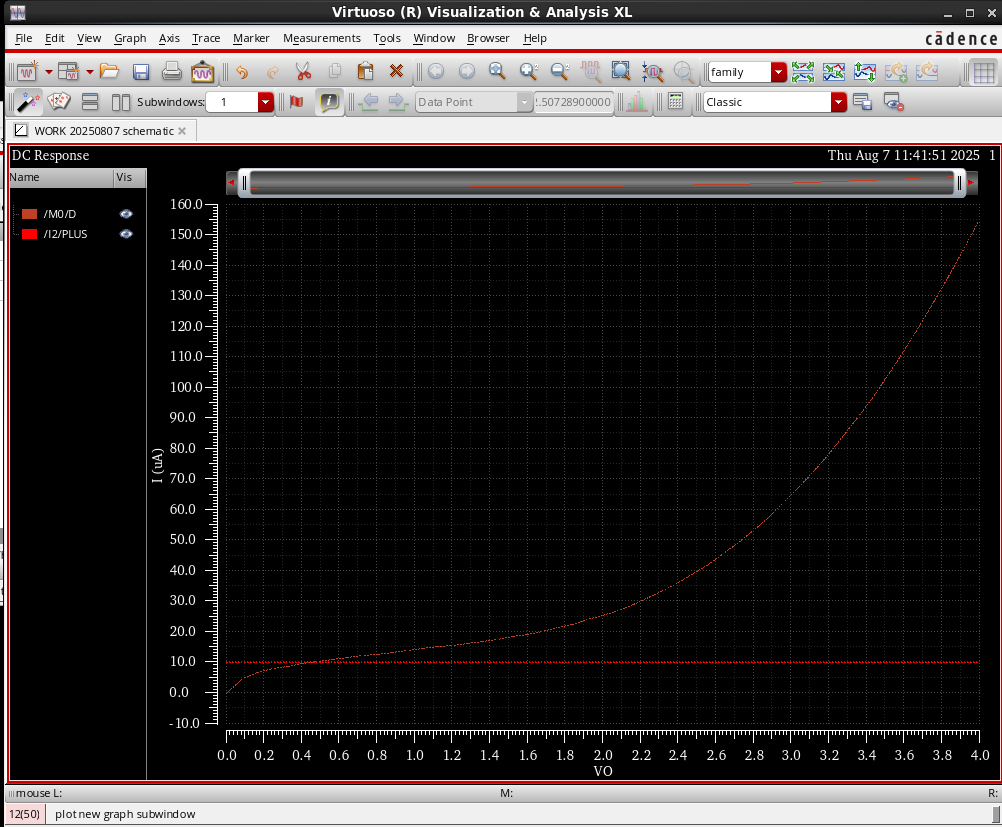

MOS管的W=100n,L=30n,电流源10uA,输出管接Vdc进行0-4V扫描,得到如下曲线(图三)

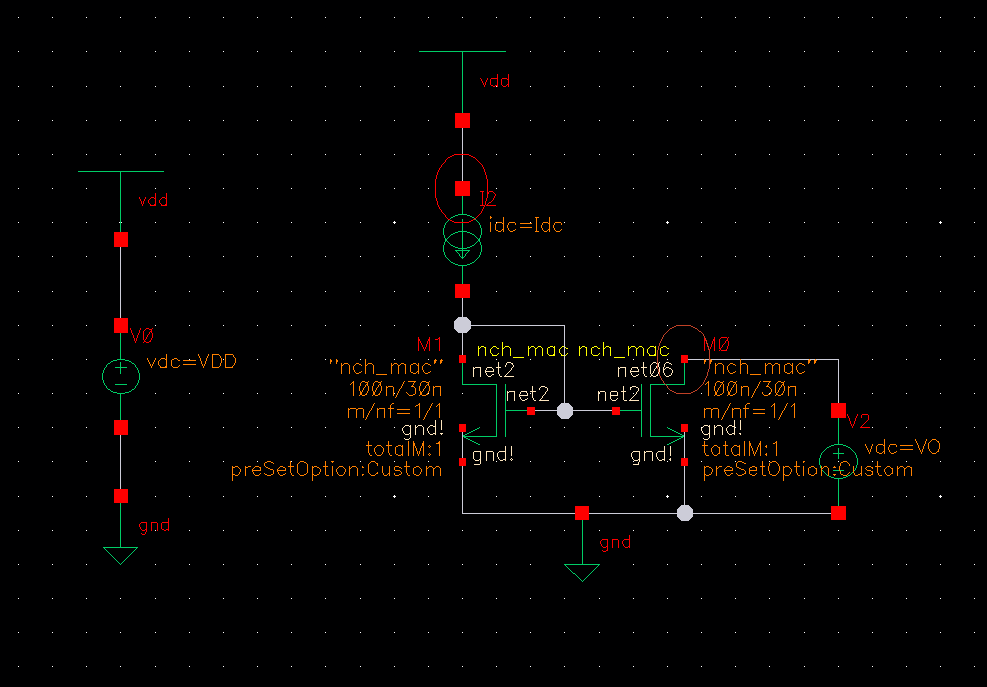

图一:原理图

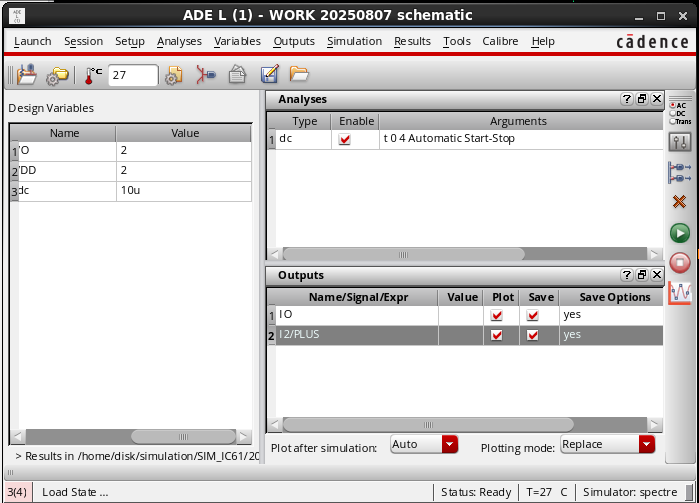

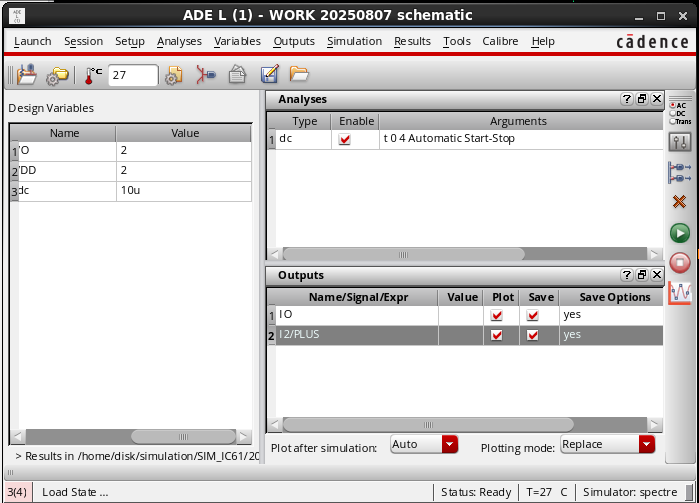

图二:相关参数:VDD=2V,对VDC进行0-4V扫描

图三:电流随VDC变化曲线

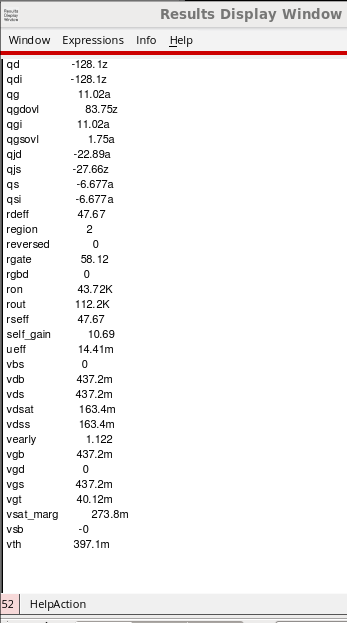

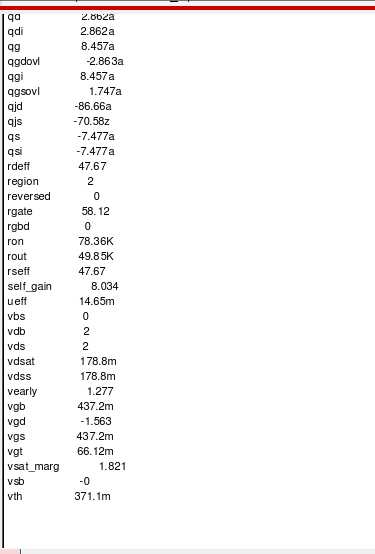

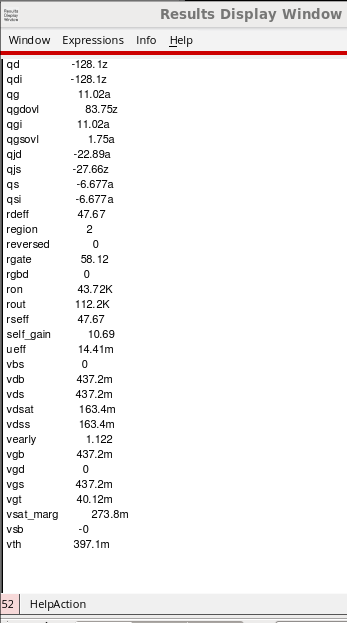

图四:M1参数

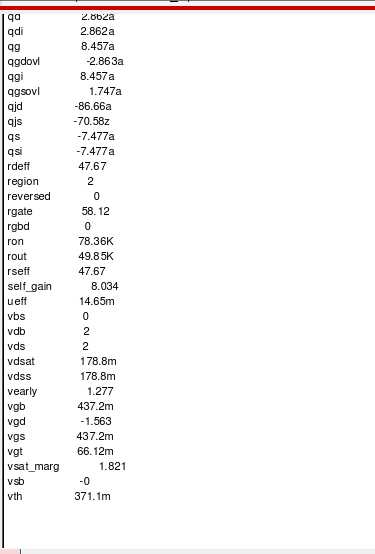

图五:MO参数

问题:输出曲线应该在进入饱和区后大致等于10uA,但是看输出曲线是一直上升的,不知道怎么解释,deepseek说是异常的,哪怕被击穿也不会到达160uA,想问下输出曲线正不正常。

MOS管的W=100n,L=30n,电流源10uA,输出管接Vdc进行0-4V扫描,得到如下曲线(图三)

图一:原理图

图二:相关参数:VDD=2V,对VDC进行0-4V扫描

图三:电流随VDC变化曲线

图四:M1参数

图五:MO参数

中午好🌞🌞🌞

本答案参考通义千问

根据你提供的信息,我们可以逐步分析输出曲线异常的原因,并给出解决方案。

MOS管参数:

预期结果:

实际观察到的现象:

DeepSeek 的反馈:

// 假设 M1 是参考晶体管,M2 是复制晶体管

M1 n1 n2 n3 gnd NMOS W=100n L=30n

M2 n4 n2 n5 gnd NMOS W=100n L=30n

.model NMOS NMOS (VTO=0.45 UO=350 LAMBDA=0.01)

* TSMC 28nm Current Mirror Simulation

.model NMOS NMOS (VTO=0.45 UO=350 LAMBDA=0.01)

VDD VDD 0 DC 3V

VDC VDC 0 DC 0V

IBIAS IBIAS 0 DC 10uA

M1 IBIAS VDC VDC 0 NMOS W=100n L=30n

M2 VOUT VDC VDC 0 NMOS W=100n L=30n

RLOAD VOUT 0 1k

* 设置直流扫描

.dc VDC 0 4 0.1

* 设置仿真选项

.options post=1

.end

注意:以上代码是一个简化版示例,具体仿真需根据实际电路结构进行调整。

你的输出曲线确实存在异常,主要原因是:

建议按照上述步骤逐一排查,特别是检查 MOS 管的工作状态和电流镜的比例一致性。如果仍然无法解决问题,可提供完整的仿真文件或原理图进一步分析。