下午好🌅🌅🌅

本答案参考通义千问

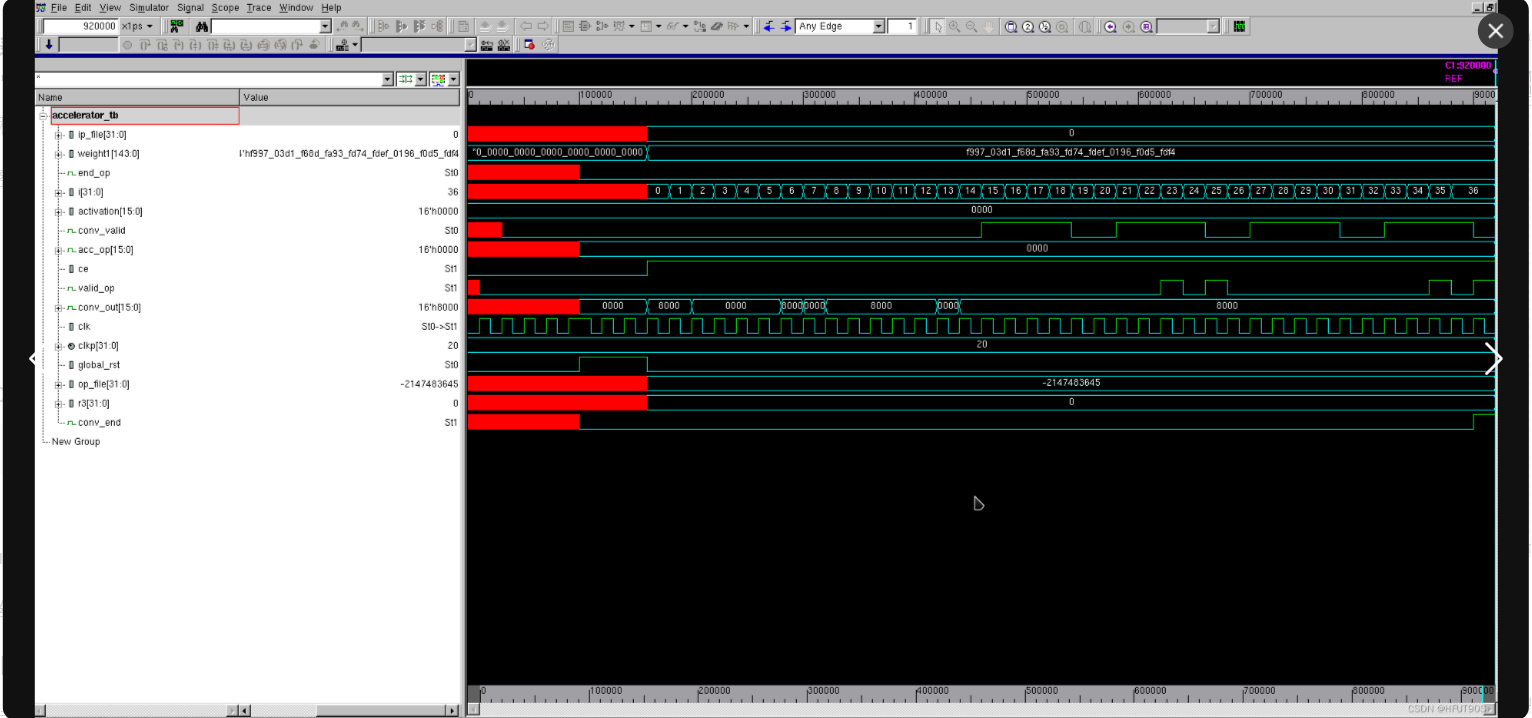

你好,感谢你的详细提问。根据你提供的信息,我理解你现在正在使用 Synopsys VCS 工具进行数字IC实践项目(CNN加速器)的复现,遇到了一些问题。以下是我对你提出的问题的详细解答。

一、关于VCS验证结果图的解读

1.1 验证结果图的作用

在数字IC设计中,VCS 是一个强大的仿真工具,用于验证设计的功能是否符合预期。验证结果图通常包括:

- 输入信号波形(如:

input_data, start_signal, clk, rst_n 等) - 输出信号波形(如:

output_result, ready_flag, valid_output 等) - 中间寄存器/状态机状态变化

- 时序关系(如:时钟边沿、信号延迟等)

1.2 如何解读这些波形?

你可以按照以下步骤进行分析:

第一步:查看时钟和复位信号

clk:表示系统时钟,是整个设计运行的基础。rst_n:复位信号,低电平有效,确保模块在初始状态下处于已知状态。

第二步:观察输入数据流

input_data:这是卷积核运算的输入数据。start_signal:触发卷积计算的信号,当它变为高电平时,开始处理输入数据。valid_input:表示当前输入数据是否有效。

第三步:查看中间状态

state_machine:状态机的状态变化,用于控制整个卷积运算流程。counter:计数器,用于控制输入数据的读取或输出数据的生成。

第四步:检查输出结果

output_result:卷积运算后的结果。ready_flag:表示输出结果是否已经准备好,可以被读取。

第五步:比较实际输出与预期结果

- 如果你在测试平台中定义了预期输出(比如通过

expected_output),可以通过将 output_result 与 expected_output 对比来判断设计是否正确。

重点总结:

- 验证结果图是用来确认设计功能是否正确的重要手段。

- 波形中的时序关系、状态变化、输入输出匹配是关键分析点。

二、如何修改输入并重新验证?

2.1 修改输入数据的路径

要修改输入数据,你需要找到测试平台(testbench)中定义输入的部分。通常是在 .v 或 .sv 文件中,例如:

// testbench.v

reg [7:0] input_data;

reg start_signal;

reg rst_n;

initial begin

rst_n = 0;

#10 rst_n = 1;

start_signal = 0;

#20 start_signal = 1;

#50 start_signal = 0;

// 设置输入数据

input_data = 8'hAA; // 这里可以修改为其他值

#100 input_data = 8'h55;

// 更多输入...

end

重点总结:

- 修改输入数据应定位到 testbench 中的

input_data 赋值部分。 - 注意时序,确保输入数据在

start_signal 激活前准备好。

2.2 修改后重新编译和仿真

完成修改后,你需要执行以下步骤:

-

重新编译代码:

vcs -R -sverilog your_module.sv testbench.v

-

运行仿真:

./simv

-

查看新的波形结果:

使用 vcd 文件或者直接在 VCS 的 GUI 中查看波形。

2.3 建议:使用脚本自动化测试

如果你希望多次测试不同输入,可以编写一个简单的 Tcl 脚本或 shell 脚本来自动切换输入数据并运行仿真。

三、关于联系博客作者的建议

由于你提到误发了一张图片导致无法回复,这里提供几个可能的联系方式:

- CSDN私信:你可以尝试再次发送私信,说明情况,并附上相关截图或说明。

- 博客评论区:在文章下方留言,询问作者是否能帮助你。

- GitHub/GitLab:如果该开源项目有对应的仓库(如 GitHub),可以去其仓库页面提交 issue 或联系作者。

重点总结:

- 建议通过多个渠道尝试联系作者,以提高成功概率。

- 在留言中清晰描述问题,并附上相关截图或代码片段,有助于作者快速理解你的需求。

四、总结

| 问题 | 解答 |

|------|------|

| 问题一:VCS验证结果图怎么解读? | 通过查看时钟、复位、输入、输出、状态机等波形,对比实际与预期结果来判断设计是否正确。 |

| 问题二:如何修改输入并重新验证? | 在 testbench 中修改 input_data 的赋值部分,然后重新编译和运行仿真。 |

如果你需要我帮你提取项目中的 testbench 文件内容,或者帮你分析某个具体波形,请提供相关代码或截图,我可以进一步协助你。

祝你项目顺利!如有更多问题,欢迎继续提问。