上午好☀️☀️☀️️

本答案参考通义千问

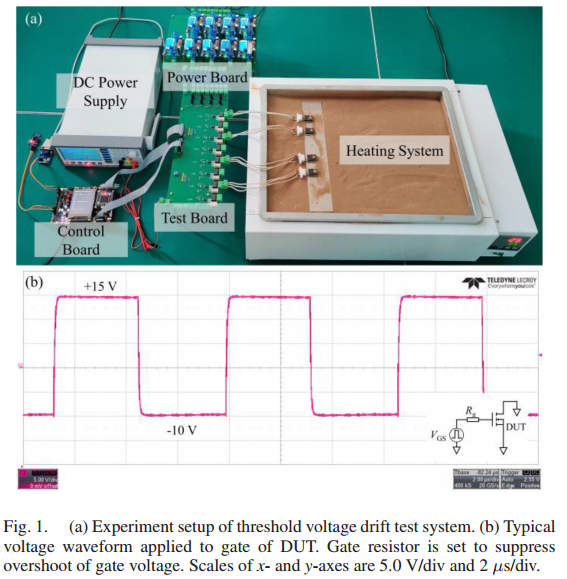

根据您的描述,这是一个针对1.2kV功率MOSFET器件的动态阈值电压漂移测试系统的设计需求。该系统需要实现一个高精度、可编程、多通道驱动电路,以支持老化、预处理、放电和阈值电压读出等不同阶段的测试流程。

一、设计目标概述

- 核心功能:实现对多个(6路)1.2kV功率MOSFET器件进行动态阈值电压漂移测试。

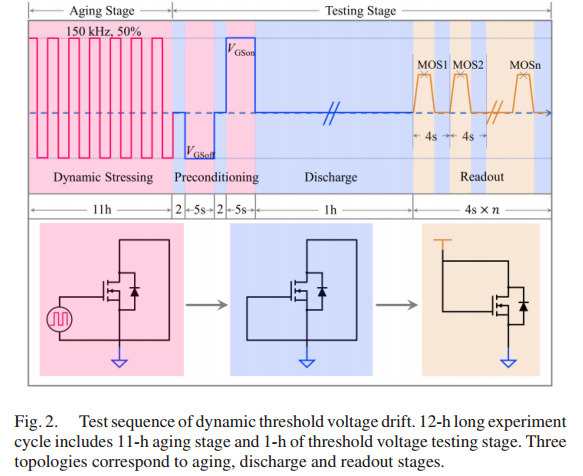

- 实验周期:

- 11小时老化阶段(交流BTI测试)

- 1小时测试阶段(包括预处理、放电、读出)

- 控制参数:

- VGSon 和 VGSoff(-10V~20V)

- 频率(0~500kHz)

- 占空比(可调)

- 驱动能力:支持6路独立驱动,每路之间留有加热装置空间

- 测试精度:阈值电压VTH定义为漏极电流ID=10mA时的栅极电压

二、硬件驱动电路设计要点

1. 栅极驱动器选择

- 关键要求:高电压耐受、快速开关、隔离能力强、低延迟

- 推荐型号(可选):

- SiC MOSFET驱动器:如 TI UCC27534 或 LTC1684

- IGBT/功率MOSFET驱动器:如 IXYS IXDD414A 或 ST IGBT Driver ICs

- 特点:

- 支持 ±15V至±20V 的栅极电压输出

- 具备 过流保护、欠压锁定、软关断 等功能

- 支持 150kHz以上的高频驱动

2. 多通道驱动设计

- 结构:采用并行驱动架构,每路独立控制

- 布局:每路之间留出至少2cm的间隙,便于散热或安装加热装置

- 通信接口:使用 SPI/I²C/RS485 接口与主控单元通信

- 同步机制:确保所有通道在相同时间点启动/停止,避免相位偏差

3. 动态栅极电压生成

- 信号源:使用 可编程函数发生器(如 Siglent SDS1202X-E) 或 FPGA + DAC 实现

- 波形类型:方波(占空比可调),频率范围 0~500kHz

- 控制逻辑:

- 老化阶段:固定50%占空比,VGSon/VGSoff可调

- 测试阶段:通过软件切换不同拓扑(老化、预处理、放电、读出)

4. 阈值电压测量模块

- 测量方式:

- 漏极电流ID通过 电流检测电阻+运算放大器 测量

- 栅极电压VGS通过 分压电路+ADC 测量

- 精度要求:

- ID测量误差 < 1%

- VGS测量误差 < 0.1V

- 数据采集:使用 ADC芯片(如 ADS1118) 进行高速采样

三、测试流程顺序说明

1. 老化阶段(11小时)

- 波形:固定50%占空比的方波

- VGSon 和 VGSoff:可调(-10V~20V)

- 频率:150kHz(加速老化)

- 目的:模拟器件在长期工作下的退化过程

2. 预处理阶段(2次5秒偏压 + 2秒零偏压)

- 波形:与老化阶段相同

- 作用:使所有DUT处于相同的初始状态,提高测试重复性

3. 放电阶段(1小时)

- 操作:将所有电极接地,消除残留电荷

- 目的:保证后续阈值电压测量的一致性

4. 阈值电压读出(连续扫描)

- 步骤:

- 对DUT施加逐步增加的栅极电压

- 监测漏极电流ID

- 当ID = 10mA时,记录此时的VGS作为VTH

- 扫描间隔:2秒一次

- 持续时间:2秒/次 × 多次(视需而定)

四、关键电路设计示例(代码/原理图参考)

1. 栅极驱动电路(简化版)

+15V

│

├─> [MOSFET] (IRF540N) → 栅极

│

├─> [驱动器IC] (UCC27534)

│

└─> [PWM信号输入] (来自FPGA或单片机)

2. 电压扫描电路(用于VTH测量)

+20V

│

├─> [DAC] (如 MCP4922) → 控制栅极电压

│

├─> [分压电阻网络] → 测量VGS

│

└─> [ADC] (如 ADS1118) → 输入到MCU

3. 漏极电流检测电路

+12V

│

├─> [电流检测电阻] (Rshunt = 0.1Ω)

│

├─> [运放] (如 OPA2376) → 放大电流信号

│

└─> [ADC] → 输入到MCU

五、系统集成建议

1. 主控单元

- 使用 嵌入式开发板(如 STM32F4、ESP32、Zynq UltraScale+ MPSoC)作为主控

- 功能:

- 控制PWM波形生成

- 读取ADC数据

- 实现逻辑控制(老化→预处理→放电→读出)

- 与上位机通信(如 LabVIEW、Python脚本)

2. 软件控制逻辑(伪代码)

def test_sequence():

# 老化阶段

set_pwm_frequency(150e3)

set_duty_cycle(50)

set_vgs_on(VGSon)

set_vgs_off(VGSoff)

start_pwm()

time.sleep(11*3600) # 11小时

# 预处理阶段

for _ in range(2):

apply_bias(VGSon, 5)

apply_bias(VGSoff, 5)

time.sleep(2)

# 放电阶段

apply_zero_bias(3600) # 1小时

# 阈值电压读出

for _ in range(10): # 10次扫描

scan_vth()

time.sleep(2)

def scan_vth():

vgs = 0

while True:

set_vgs(vgs)

id = read_adc_current()

if id >= 10e-3: # 10mA

print("VTH =", vgs)

break

vgs += 0.1 # 步进0.1V

六、注意事项

- 安全防护:由于是高压(1.2kV)设备,必须做好绝缘、隔离、保护电路设计

- 散热设计:每个驱动通道之间留有足够间隙,防止热量集中

- EMI抑制:使用屏蔽线缆、滤波电容、地线优化等手段降低电磁干扰

- 校准:定期校准ADC、DAC、电流检测模块,确保测量精度

七、总结

| 项目 | 内容 |

|------|------|

| 驱动器 | 可编程、隔离型、高耐压 |

| 波形生成 | 方波(50%占空比),频率可调(0~500kHz) |

| 测试流程 | 老化 → 预处理 → 放电 → 读出 |

| 测量精度 | VTH误差 < 0.1V,ID误差 < 1% |

| 多通道 | 支持6路独立驱动,留有加热间隙 |

如您需要,我可以提供完整的电路原理图、PCB布局建议、代码框架以及测试报告模板。欢迎继续提问!