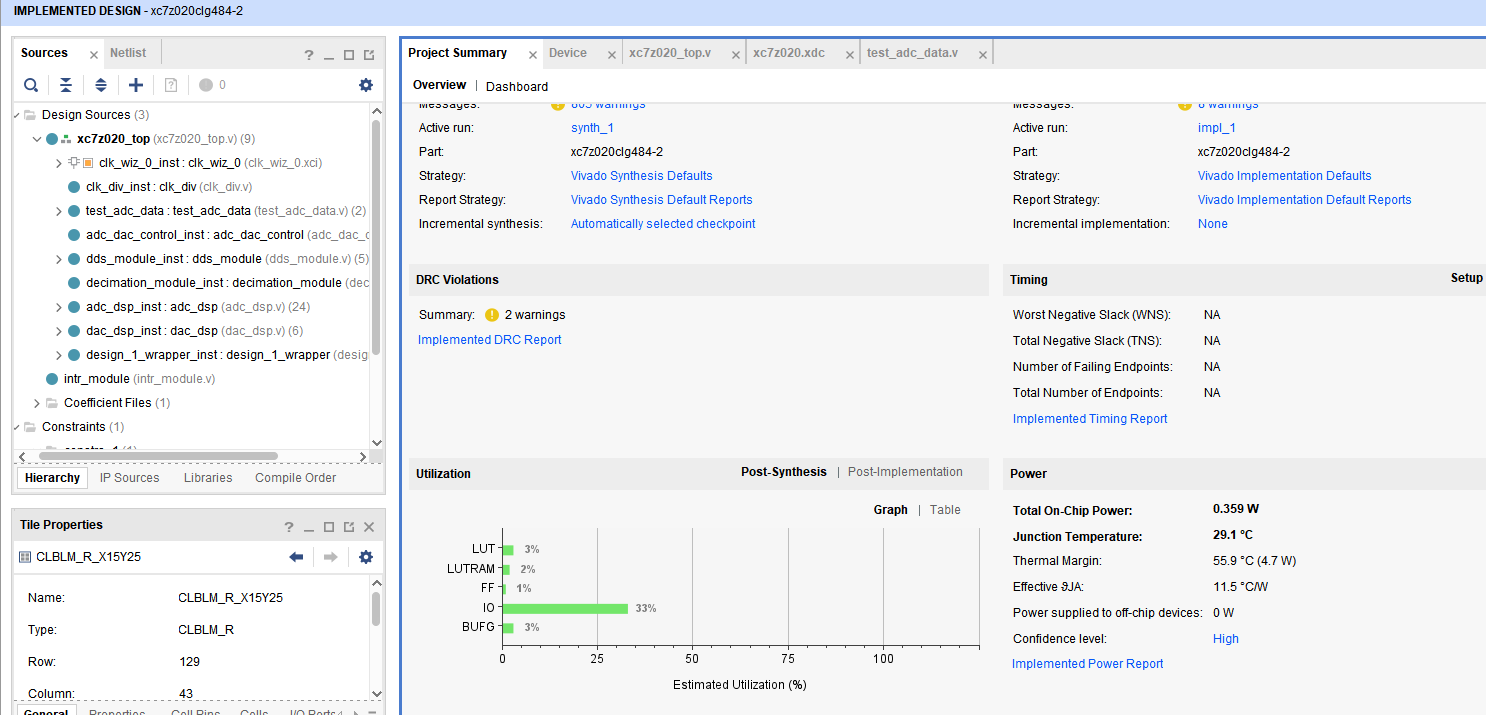

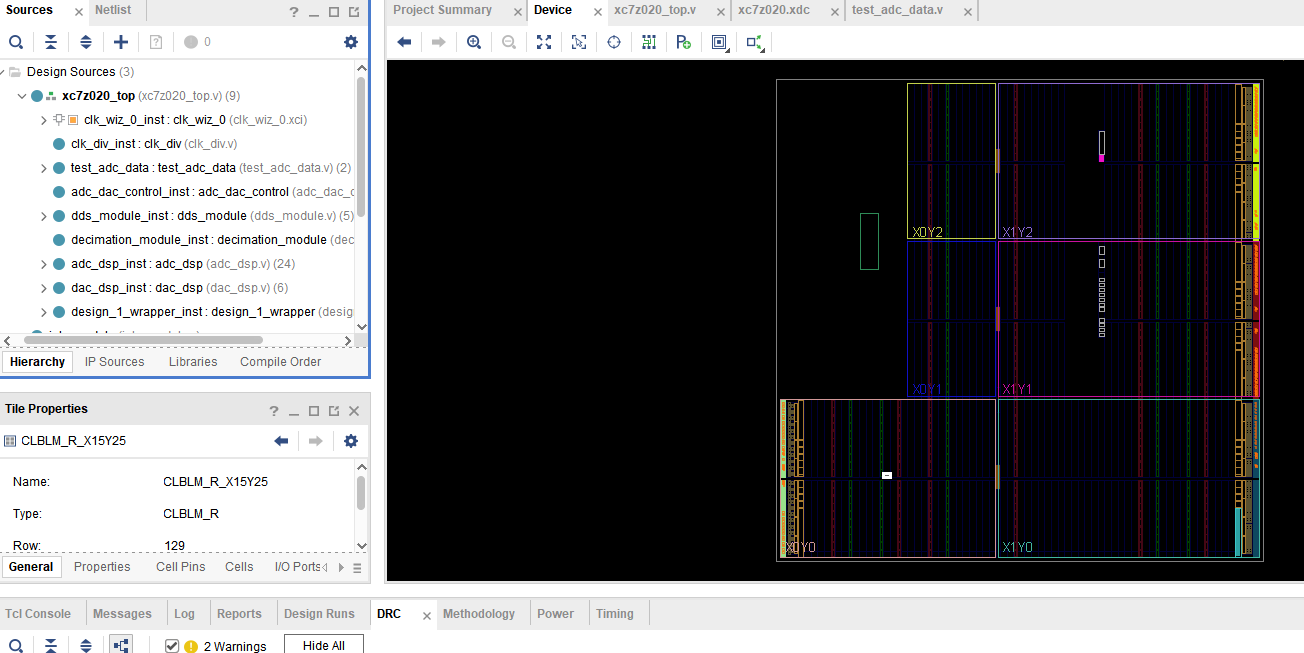

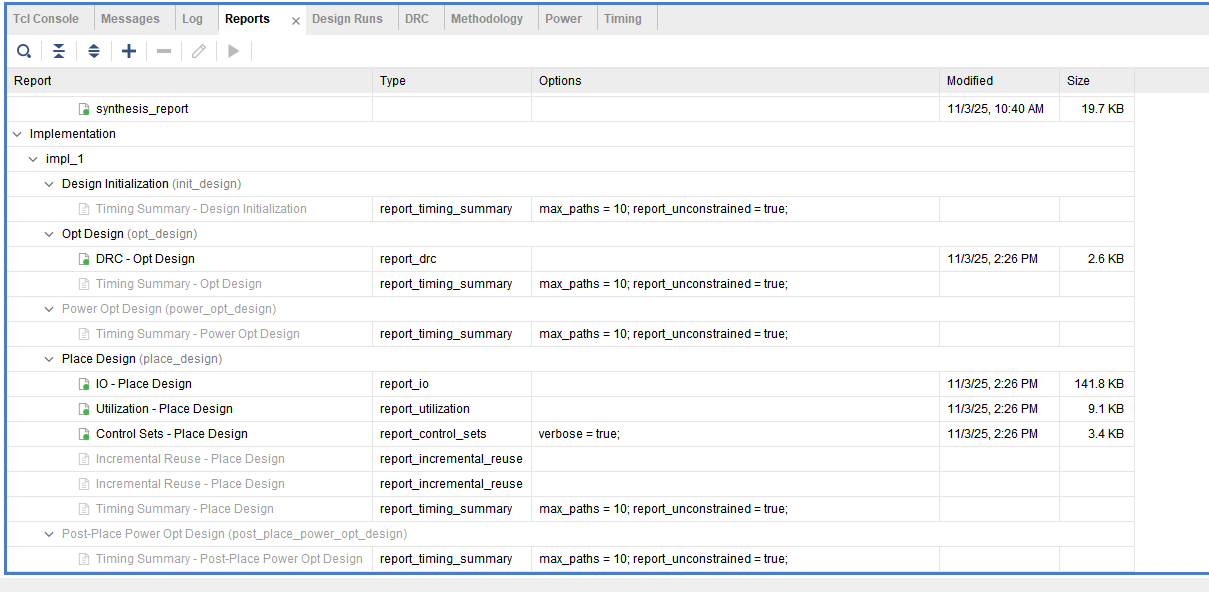

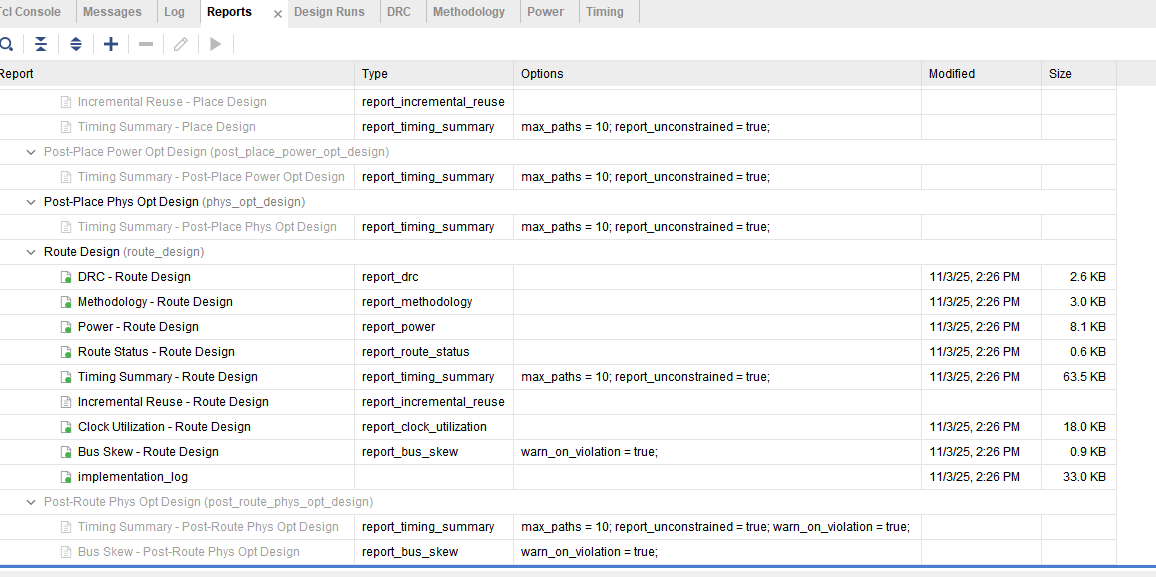

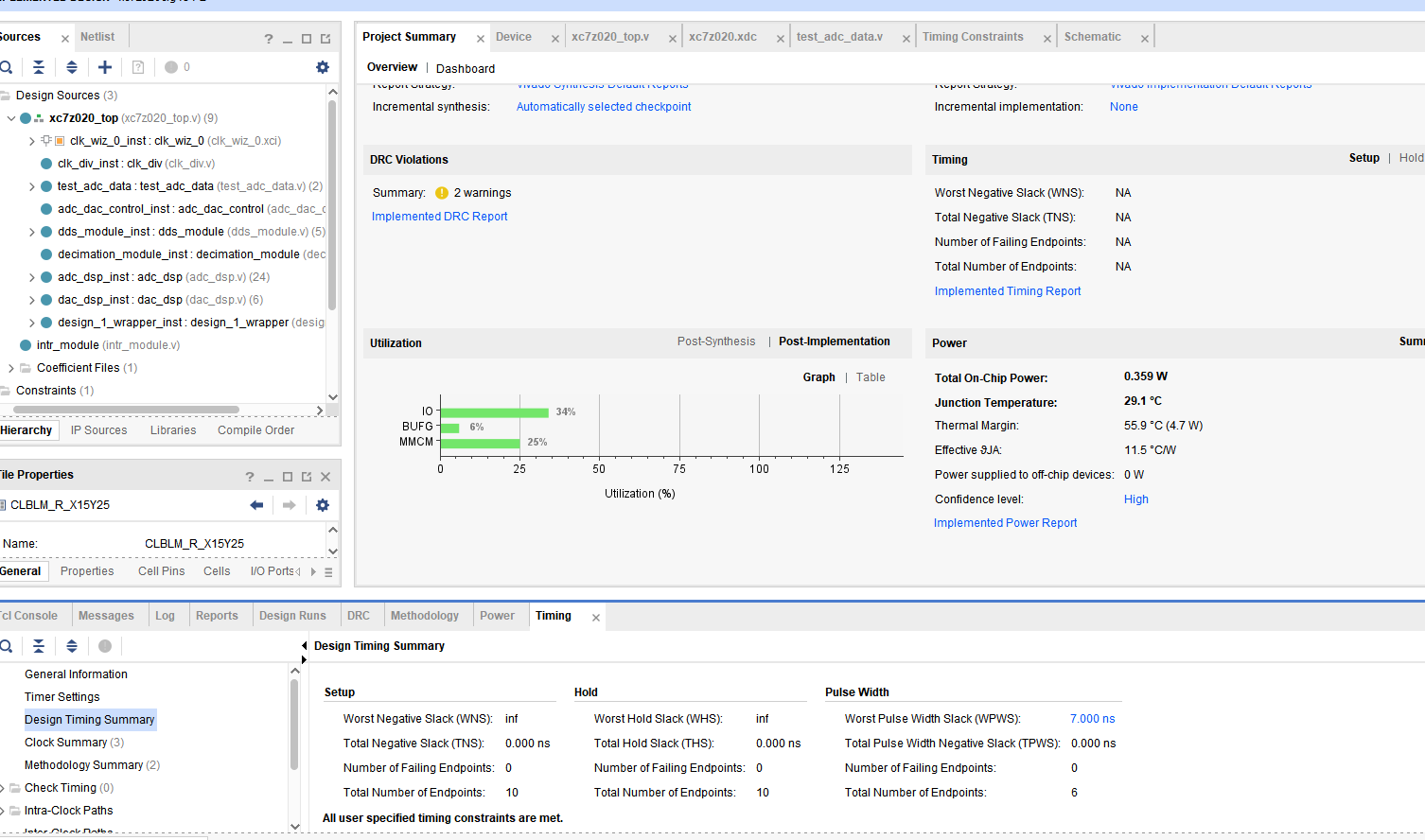

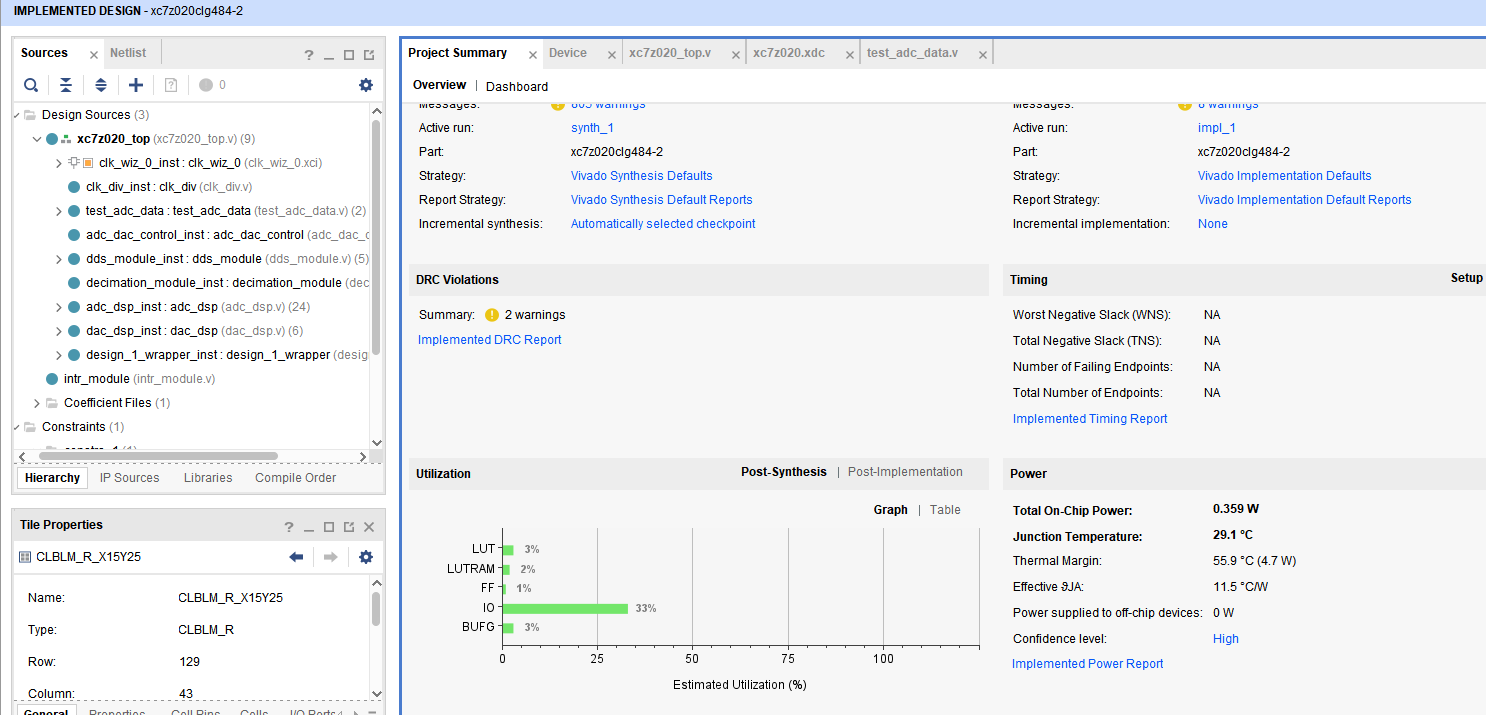

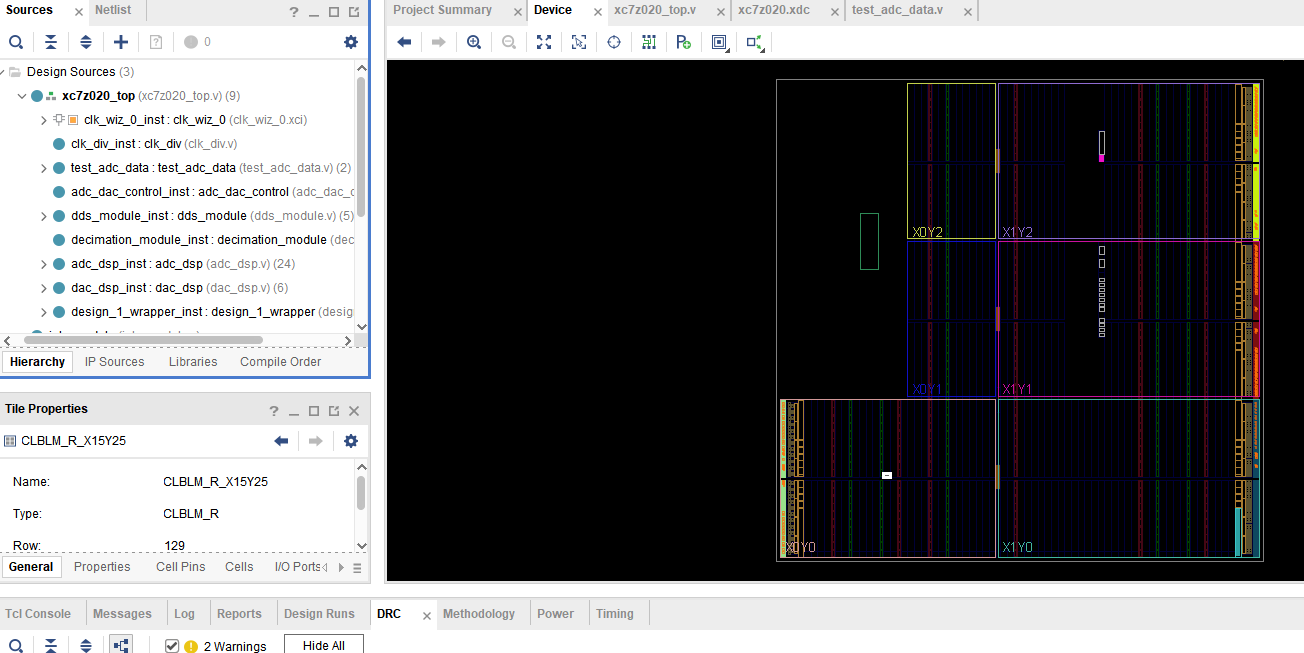

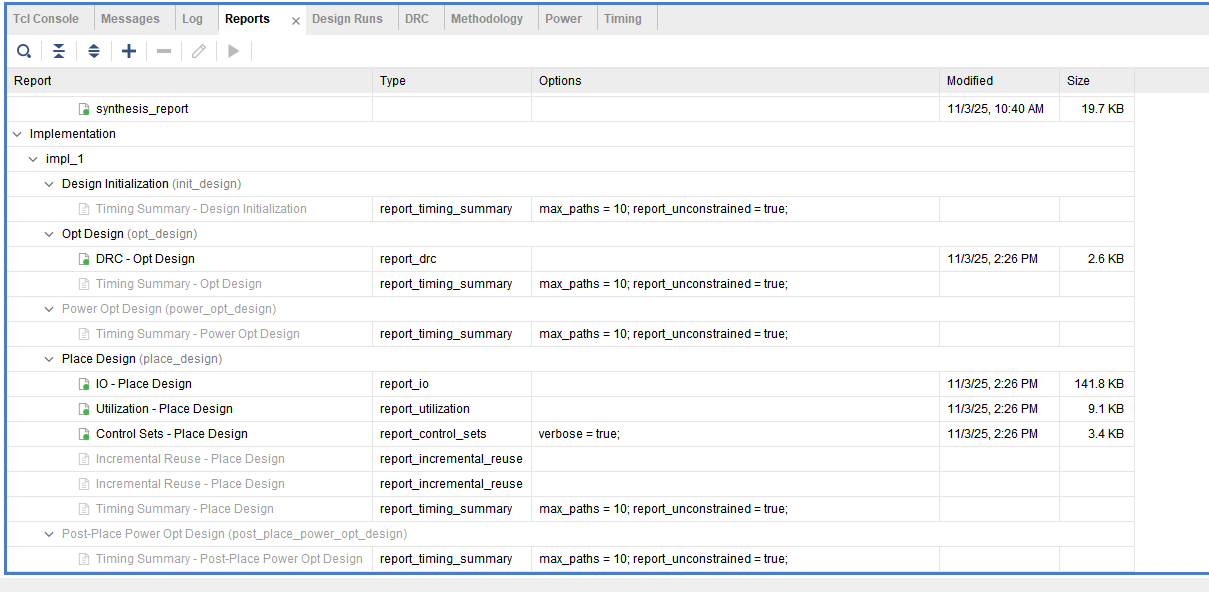

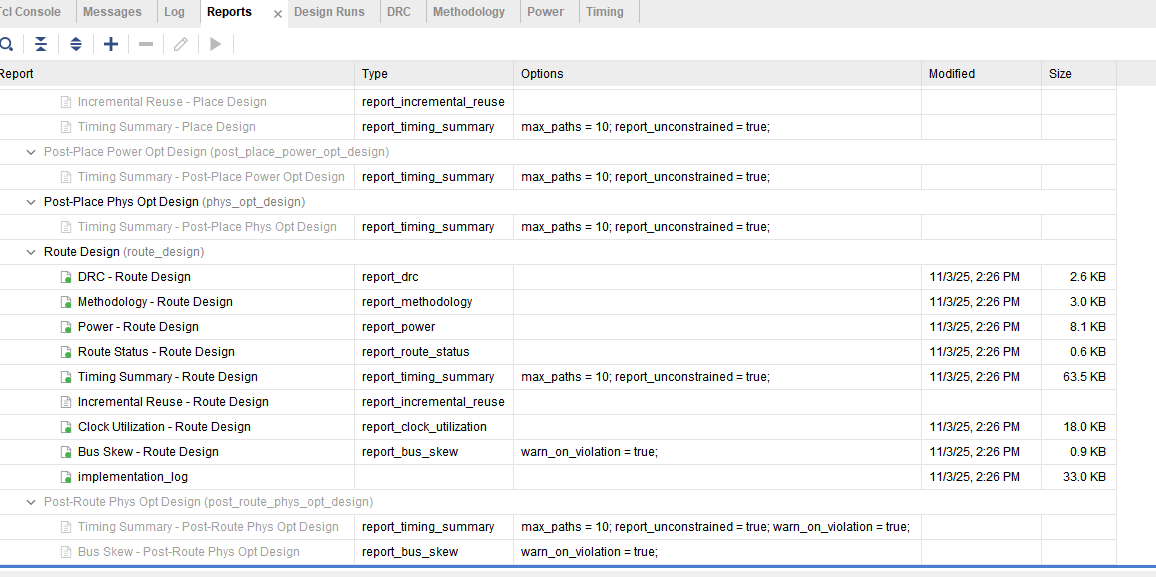

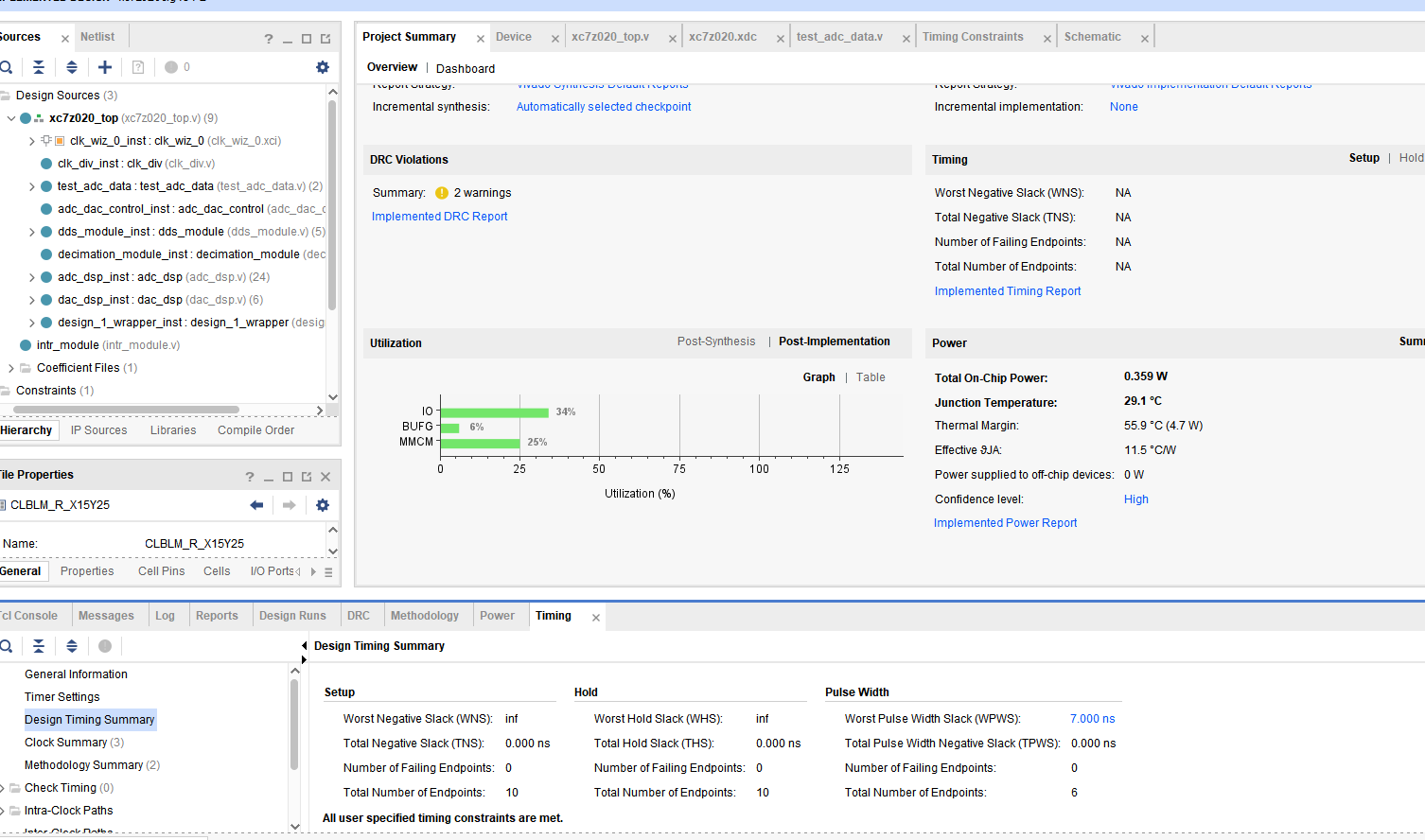

如图,vivado新建的工程,DDS/FIR等功能已经进行功能仿真,确定这些功能已经完成,到了编译工程生成bit文件阶段,编译报告界面没有用到一点DSP、BRAM、LUT等资源,timing summary显示为NA,打开device界面,工程布局布线全部是空的,没有连一根线,但bit文件已经生成,很明显是哪个步骤出了问题,检查了setting-ilplementation的勾选设置,相关配置全部正确,请问哪里有问题。

如图,vivado新建的工程,DDS/FIR等功能已经进行功能仿真,确定这些功能已经完成,到了编译工程生成bit文件阶段,编译报告界面没有用到一点DSP、BRAM、LUT等资源,timing summary显示为NA,打开device界面,工程布局布线全部是空的,没有连一根线,但bit文件已经生成,很明显是哪个步骤出了问题,检查了setting-ilplementation的勾选设置,相关配置全部正确,请问哪里有问题。

阿里嘎多学长整理AIGC生成,因移动端显示问题导致当前答案未能完全显示,请使用PC端查看更加详细的解答过程

问题分析

根据你的描述,Vivado布局布线失败,编译报告界面显示没有使用到DSP、BRAM、LUT等资源,timing summary也没有显示。这种情况通常是因为设计没有正确地使用这些资源,或者是资源分配不合理。

解决方案

核心代码

-- 检查资源分配

entity my_design is

Port (

-- DSP输入端口

clk : in STD_LOGIC;

rst : in STD_LOGIC;

-- DSP输出端口

output : out STD_LOGIC

);

end my_design;

architecture Behavioral of my_design is

-- DSP实例

signal dsp_out : STD_LOGIC;

begin

-- DSP功能

dsp_process : process(clk)

begin

if rising_edge(clk) then

-- DSP功能实现

dsp_out <= '1';

end if;

end process;

-- 输出端口

output <= dsp_out;

end Behavioral;

注意

上述代码仅供参考,具体的设计实现需要根据实际需求进行调整。