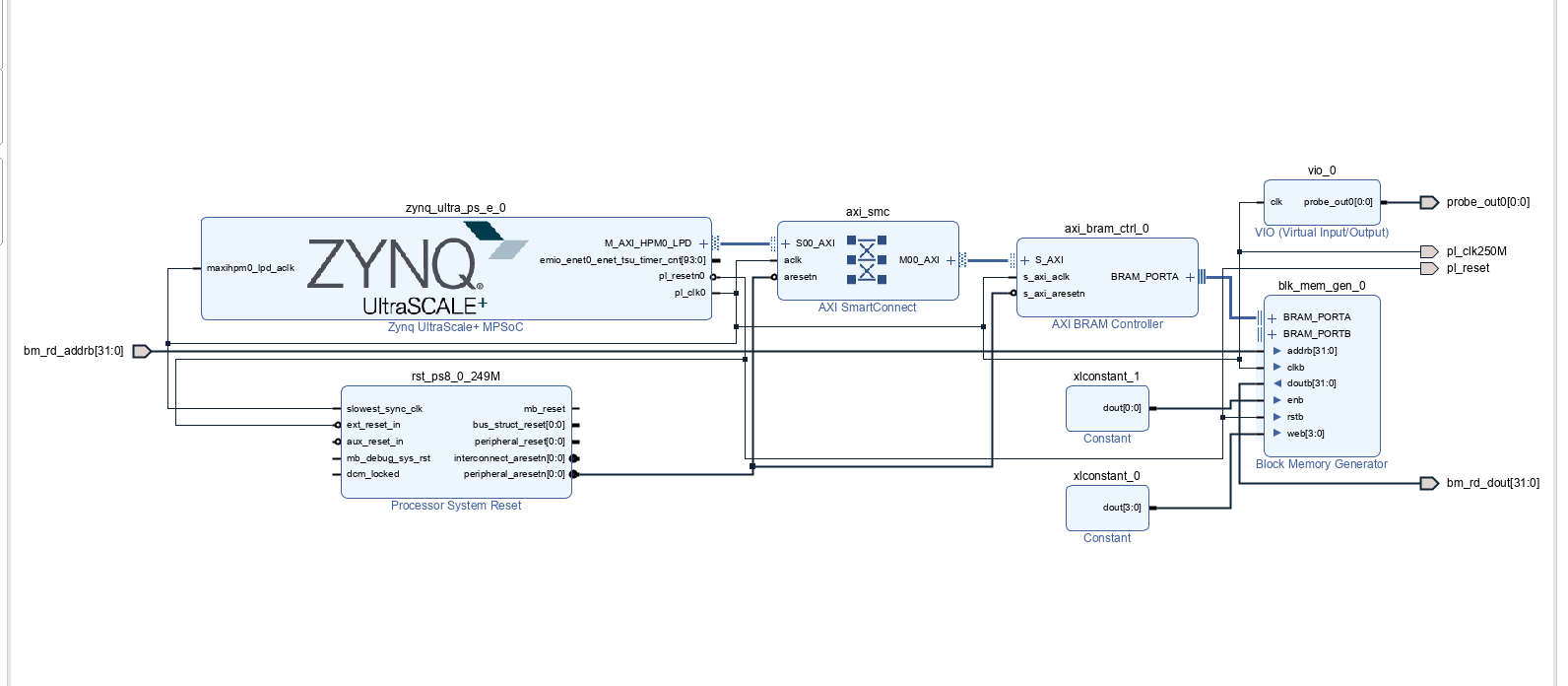

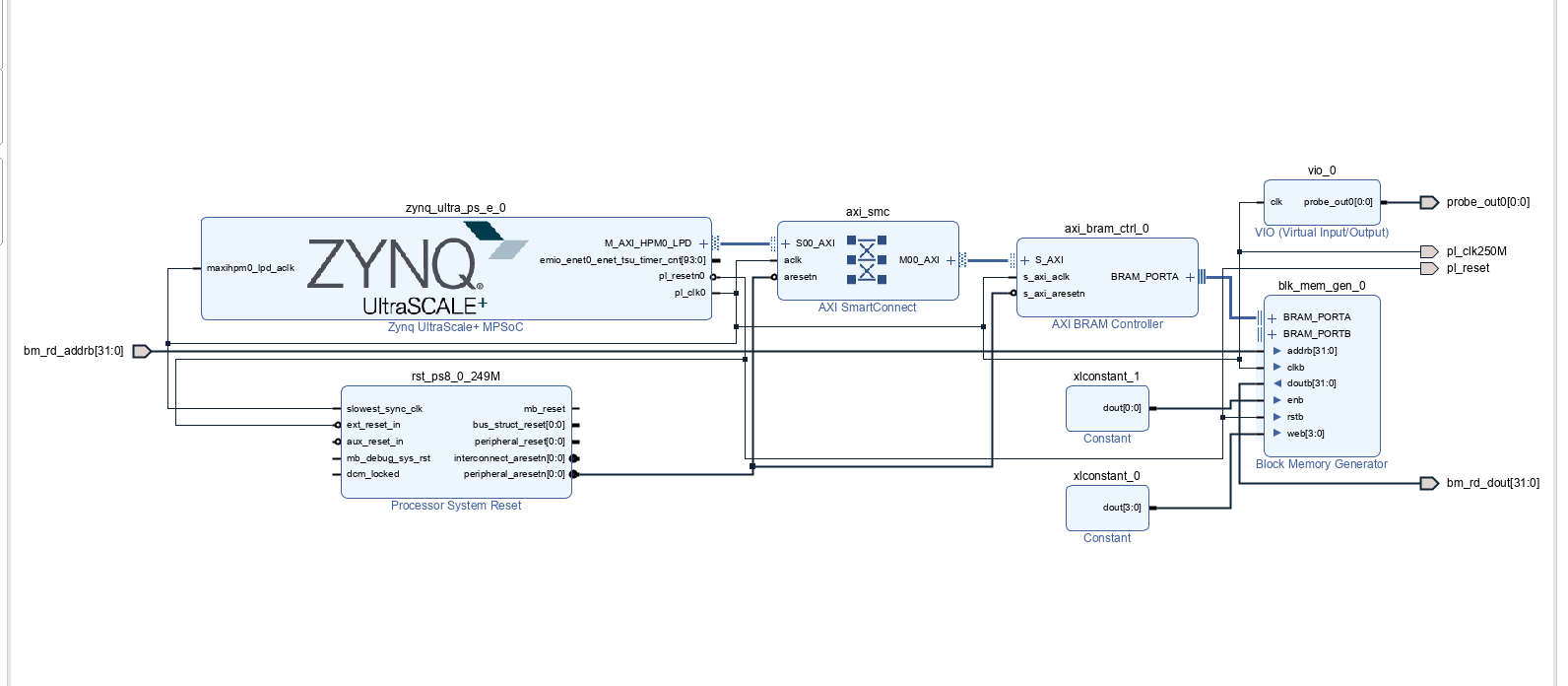

我使用bram进行PS端和PL端通信,PS端通过axi_bram_ctrl连接bram ip核,bram配置成真双端,bram_en和bram_addr都给了信号,但是无论怎么测怎么调bram读口dout都是0,我每个接口都对齐了,时钟也统一采用PS端提供给PL端的时钟,vitis代码写地址也能对应上,在memory monitor中能看到对应地址数据,但是就是dout读不出来,困扰我一周了,请问这种情况怎么办?

我使用bram进行PS端和PL端通信,PS端通过axi_bram_ctrl连接bram ip核,bram配置成真双端,bram_en和bram_addr都给了信号,但是无论怎么测怎么调bram读口dout都是0,我每个接口都对齐了,时钟也统一采用PS端提供给PL端的时钟,vitis代码写地址也能对应上,在memory monitor中能看到对应地址数据,但是就是dout读不出来,困扰我一周了,请问这种情况怎么办?

晚上好🌙🌙🌙

本答案参考通义千问

你遇到的问题是关于 Xilinx Zynq UltraScale+ MPSoC 中使用 BRAM IP核(Block RAM) 时,PS端通过AXI接口读取数据失败,即 dout始终为0。虽然你已经确认了地址、时钟、信号对齐等配置,但仍然无法读出数据。这是一个非常典型的硬件与软件协同调试问题。

重点:BRAM的读端口必须被使能才能读取数据!

重点:AXI_BRAM_CTRL 必须与 PS 端的时钟同步,并且地址映射正确。

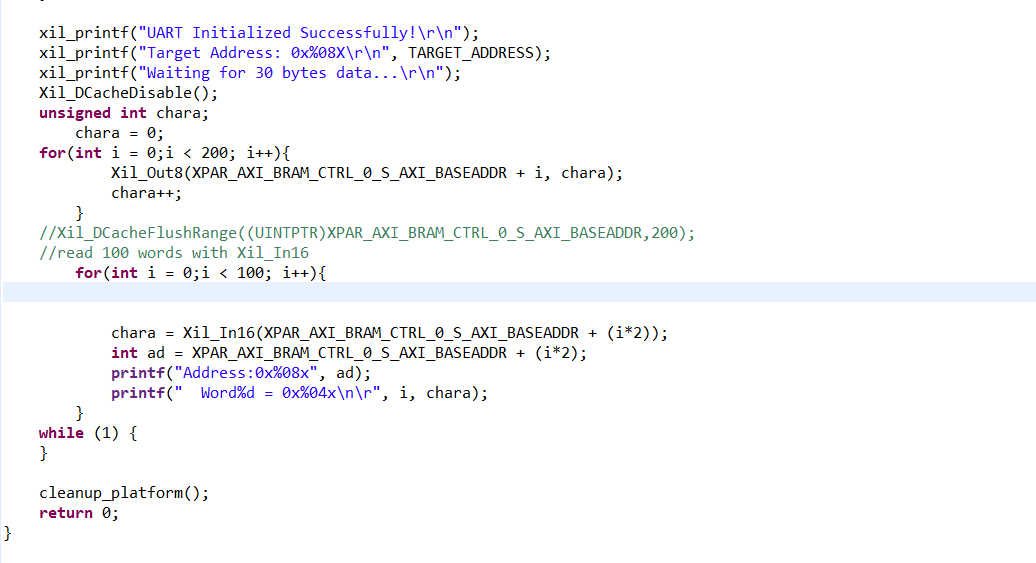

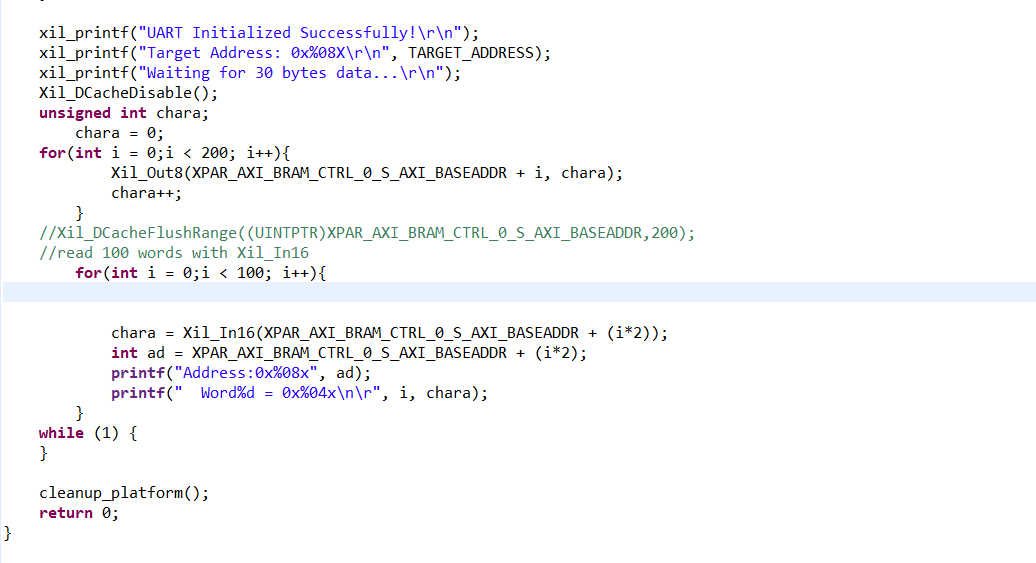

Xil_In32 或 Xil_Out32 等函数进行读写;重点:Vitis 中的内存映射必须与硬件设计中的地址匹配,否则读写无效。

以下是逐步排查和解决该问题的步骤:

重点:确保 BRAM 的读端口被使能(EN)!

MIO 或 DDR 时钟);0x4000_0000 到 0x4000_0FFF)。重点:AXI_BRAM_CTRL 必须与 PS 端时钟同步,并且地址映射正确。

#include "xaxi_bram_ctrl.h"

XAxibramctrl bram_inst;

int main() {

int status;

u32 data;

status = XAxibramctrl_Initialize(&bram_inst, XPAR_AXI_BRAM_CTRL_0_DEVICE_ID);

if (status != XST_SUCCESS) {

return XST_FAILURE;

}

// 写入数据

XAxibramctrl_WriteReg(bram_inst.BaseAddress, 0x00, 0x12345678);

// 读取数据

data = XAxibramctrl_ReadReg(bram_inst.BaseAddress, 0x00);

// 输出结果

xil_printf("Read Data: 0x%x\n", data);

return 0;

}

重点:使用

XAxibramctrl_ReadReg读取数据,而不是直接访问内存。

0x40000000),查看是否有数据。重点:Memory Monitor 只能验证硬件是否正确加载数据,不能保证软件读取有效。

S_AXI_ARESETN 是否拉高);重点:时序不匹配会导致数据读取失败。

err 或 ready 信号)。重点:仿真可以帮助定位逻辑层面的问题。

如果你使用的是自定义的 AXI 接口,可以尝试如下代码:

#include <stdio.h>

#include "xil_types.h"

#include "xil_io.h"

#define BRAM_BASEADDR 0x40000000

#define BRAM_SIZE 0x1000

void write_bram(u32 address, u32 data) {

Xil_Out32(BRAM_BASEADDR + address, data);

}

u32 read_bram(u32 address) {

return Xil_In32(BRAM_BASEADDR + address);

}

int main() {

u32 value = 0x12345678;

u32 read_value;

// 写入数据

write_bram(0x00, value);

// 读取数据

read_value = read_bram(0x00);

printf("Written: 0x%x\n", value);

printf("Read: 0x%x\n", read_value);

return 0;

}

重点:使用

Xil_Out32和Xil_In32直接操作内存地址,适用于简单测试。

| 问题点 | 原因 | 解决方法 |

|--------|------|----------|

| BRAM 读端口未使能 | EN 未连接或未启用 | 检查 BRAM IP 配置,确保读使能 |

| AXI_BRAM_CTRL 配置错误 | 地址映射错误或时钟不同步 | 检查 AXI_BRAM_CTRL 的地址和时钟 |

| Vitis 软件错误 | 使用错误的地址或读写方式 | 使用 XAxibramctrl_ReadReg 或 Xil_In32 |

| 时序问题 | 时钟不同步或复位不稳定 | 检查时钟和复位信号 |

| 仿真未验证 | 无法判断逻辑错误 | 使用 Vivado Simulator 验证逻辑 |

如果你愿意提供具体的 Vivado 工程截图、AXI_BRAM_CTRL 配置图、Vitis 代码片段,我可以进一步帮助你定位问题。希望以上内容对你有所帮助!