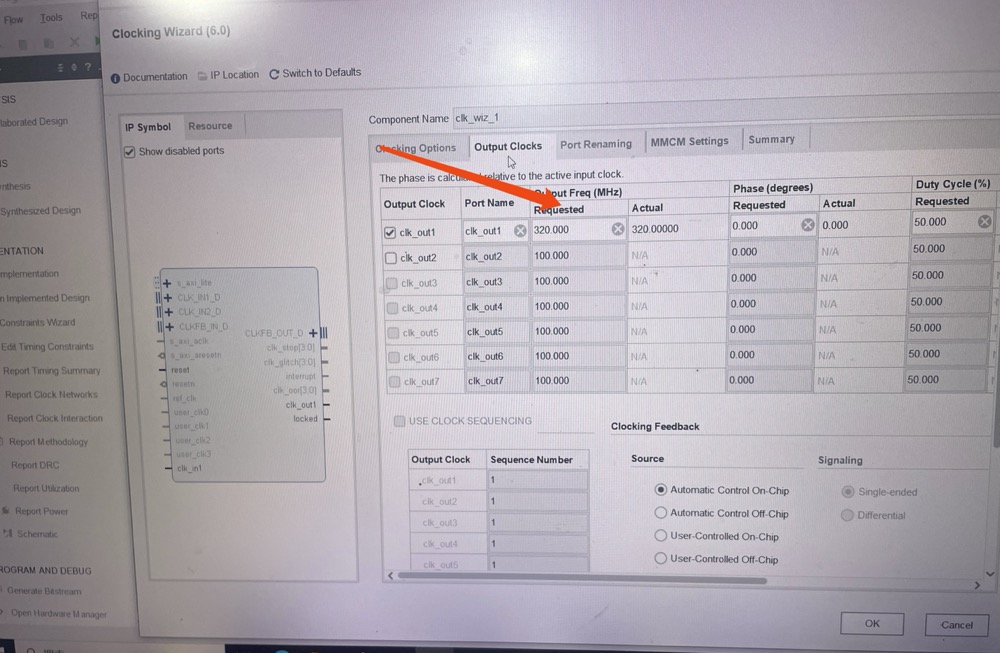

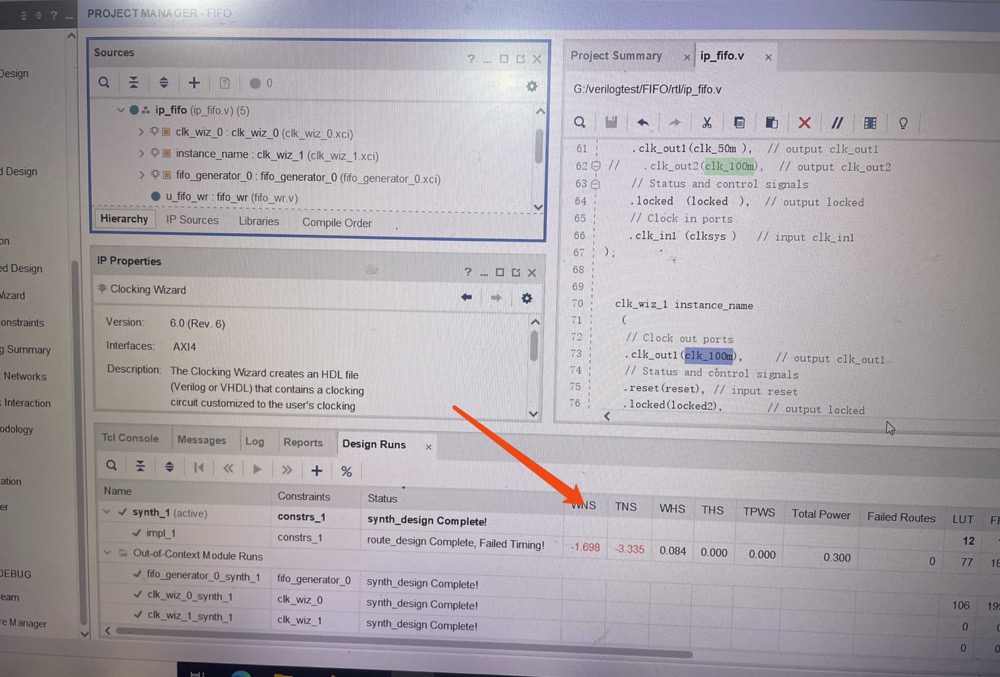

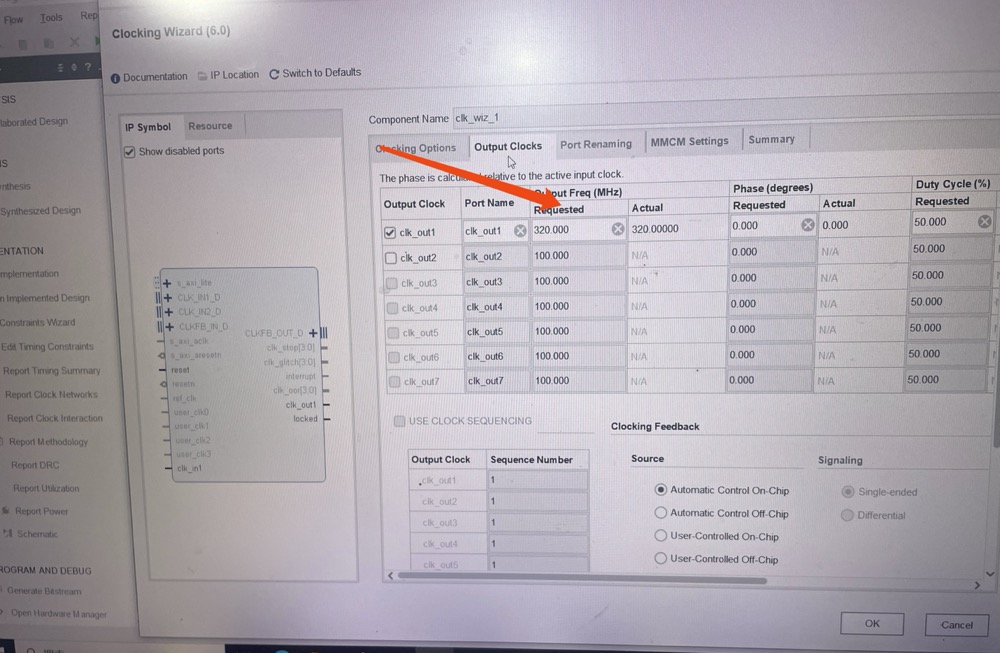

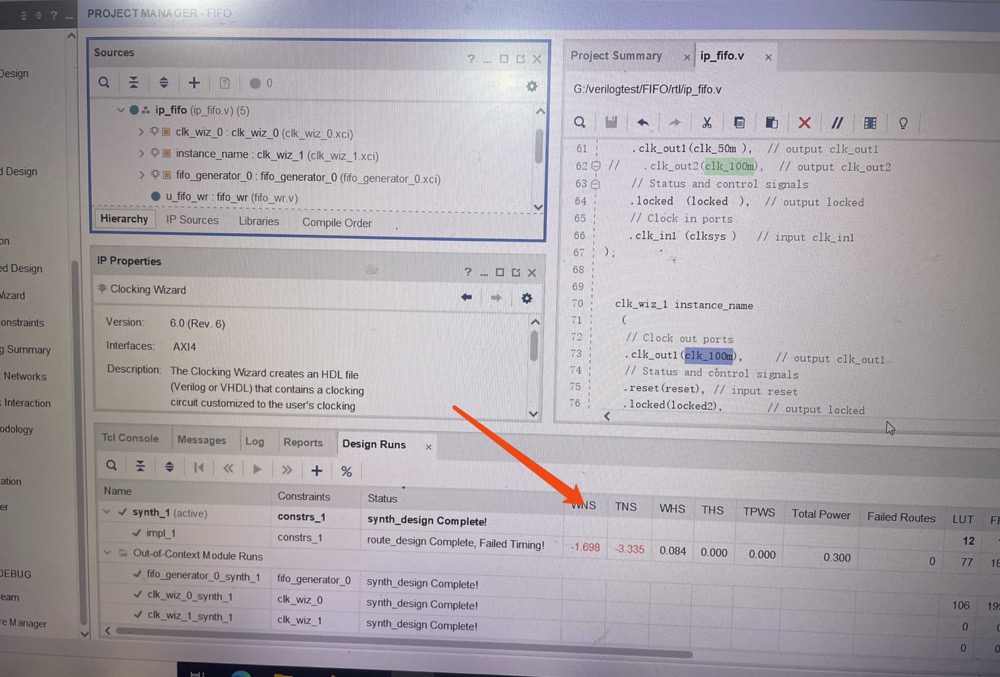

专家您好,请问下这种情况如何处理呢? 我看了您的文章https://blog.csdn.net/weixin_46423500/article/details/151834865 。生成多一个clock IP后,可以在clock生成的页面写入310M、360M等这种类型的时钟了而不报错了。但是接下来又有了新的问题,就是像图片上一样,综合实现后,提示时序违例。

请问这种情况该如何解决呢?

专家您好,请问下这种情况如何处理呢? 我看了您的文章https://blog.csdn.net/weixin_46423500/article/details/151834865 。生成多一个clock IP后,可以在clock生成的页面写入310M、360M等这种类型的时钟了而不报错了。但是接下来又有了新的问题,就是像图片上一样,综合实现后,提示时序违例。

请问这种情况该如何解决呢?

关注

关注让 “紫雾凌寒” 来帮你回答,本回答结合 DeepSeek

如果还有问题,请评论或点击头像私信,如果有帮助到您, 请关注、采纳、点赞

create_clock -name clk -period 10.000 [get_ports clk]report_timing -max_paths 10 -nworst 10verilog

module adder_pipelined (

input wire clk,

input wire [31:0] a,

input wire [31:0] b,

output reg [31:0] result

);

reg [31:0] a_pipe1;

reg [..:..] b_pipe1;

always @(posedge clk) begin

a_pipe1 <= a;

b_pipe1 <= b;

end

reg [31:0] result_pipe1;

always @(posedge clk) begin

result_pipe1 <= a_pipe1 + b_pipe1;

end

always @(posedge clk) begin

result <= result_pipe1;

end

endmoduleverilog

wire clk;

wire cl;

my_pll uut (

.clk_in1(clk),

.clk_out1(cl)

);希望以上解答对您有所帮助。如果您有任何疑问,欢迎在评论区提出。