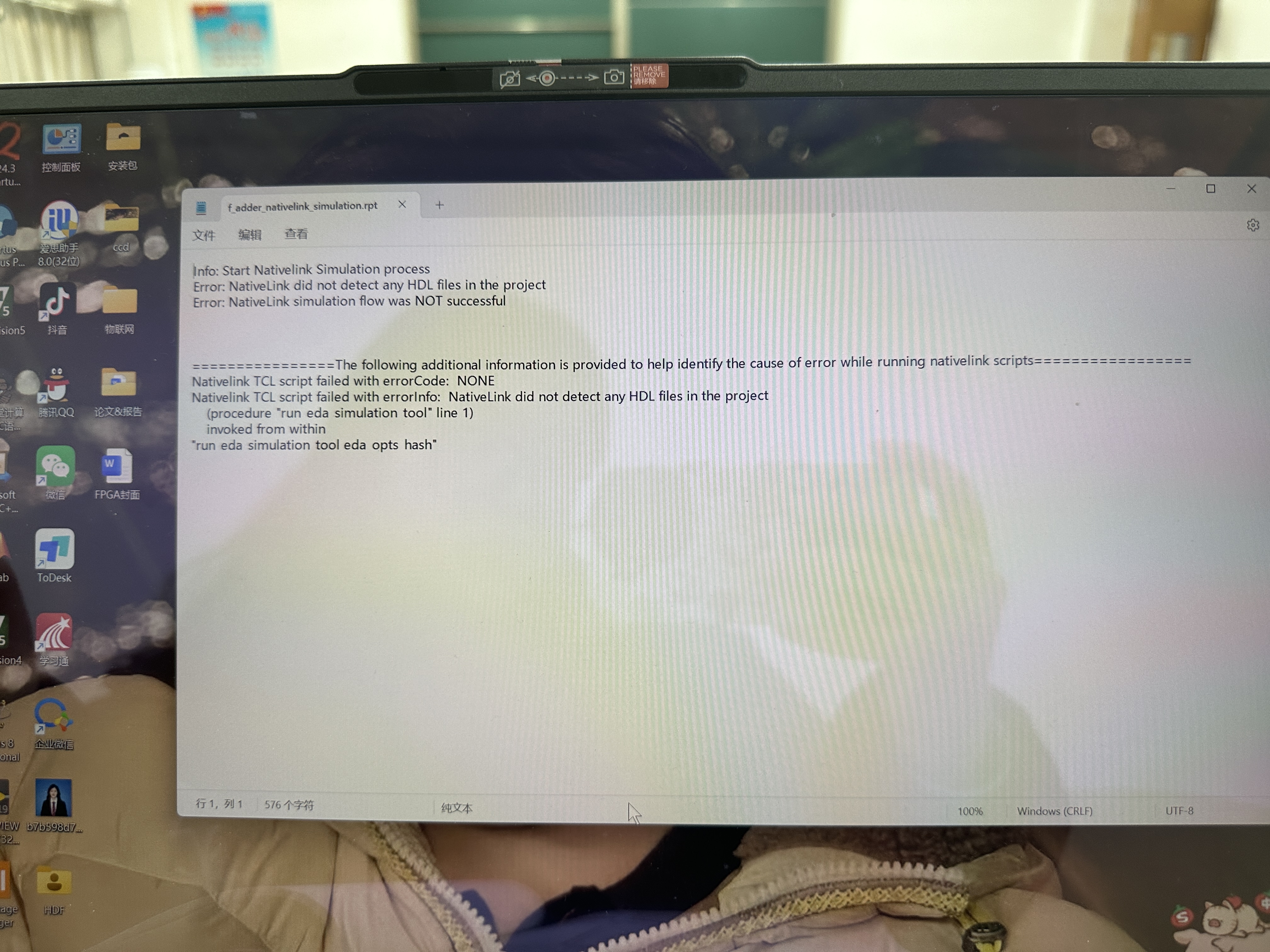

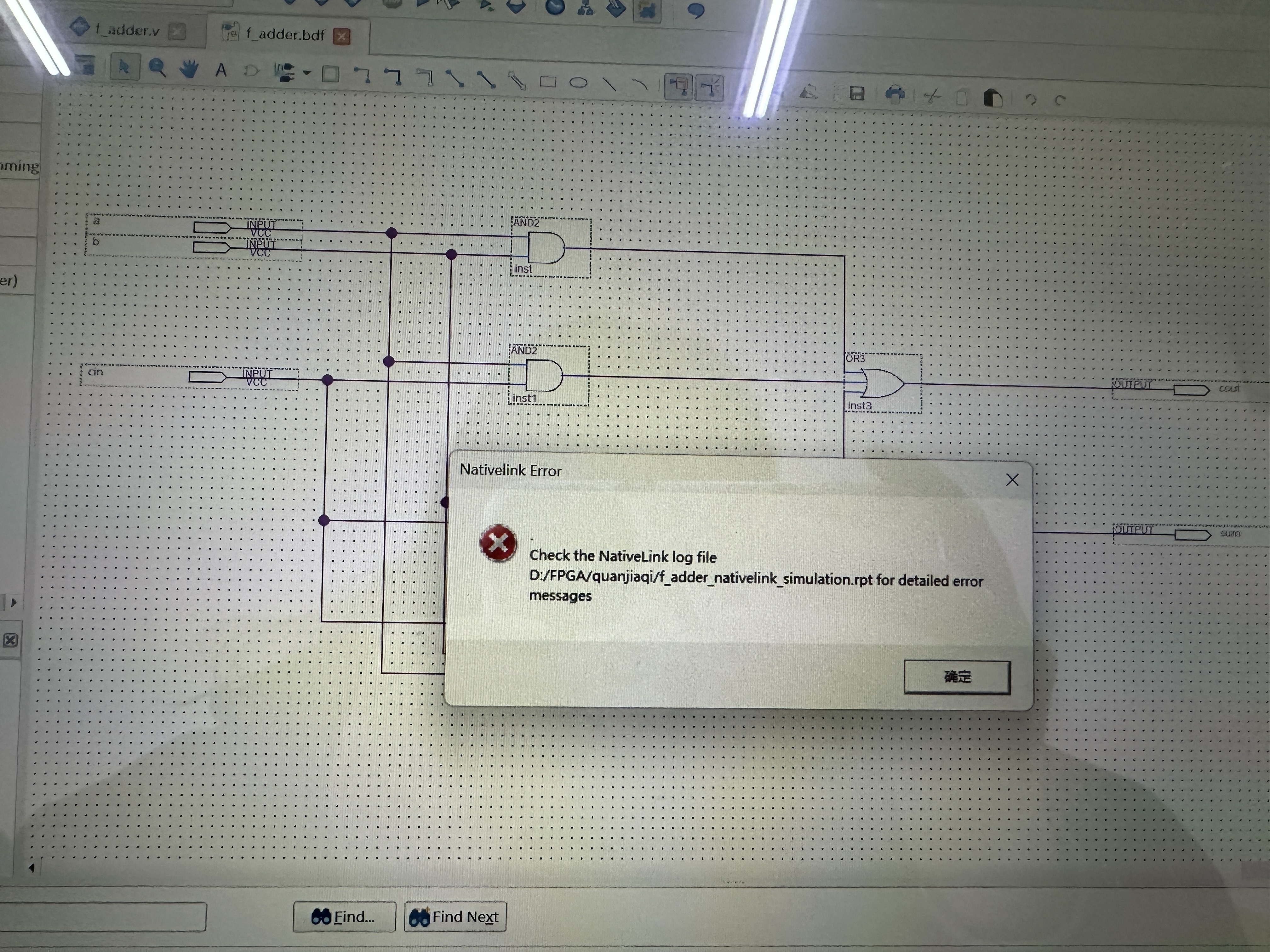

我想要完成一个全加器的功能仿真但是一直出现这个错误,添加了一个hdl后缀为.v的文件也不行

上午好☀️☀️☀️️

本答案参考通义千问

在使用 Quartus II 进行 VHDL/Verilog 设计时,如果你遇到了“错误:无法识别的文件类型或文件扩展名”或“添加了一个 .v 文件也不行”这样的问题,可能的原因包括以下几点。下面我会详细解释原因,并提供解决方案。

文件后缀不正确

.v 用于 Verilog,.vhd 用于 VHDL)。.hdl 文件,Quartus 不会识别它,因为它不是标准的 HDL 文件格式。未正确设置顶层模块

未正确设置仿真工具

未正确编译项目

文件路径或名称有特殊字符

检查文件后缀是否为 .v 或 .vhd

.v。.vhd。.hdl,因为 Quartus 不支持这种格式。将文件添加到 Quartus 项目中

.v 文件并添加进去。设置顶层模块(Top-Level Entity)

编译整个项目

设置仿真工具(可选)

运行仿真

如果你正在编写一个全加器(Full Adder),以下是完整的 Verilog 代码示例:

// full_adder.v

module full_adder (

input a,

input b,

input cin,

output sum,

output cout

);

wire xor1, xor2;

wire and1, and2, and3;

// XOR 两个输入

xor (xor1, a, b);

xor (xor2, xor1, cin);

// AND 逻辑

and (and1, a, b);

and (and2, a, cin);

and (and3, b, cin);

// OR 逻辑

or (cout, and1, or (or1, and2, and3));

assign sum = xor2;

endmodule

| 错误提示 | 原因 | 解决方案 |

|----------|------|-----------|

| “无法识别的文件类型” | 使用了 .hdl 后缀 | 改为 .v 或 .vhd |

| “找不到顶层模块” | 未设置 Top-Level Entity | 设置顶层模块 |

| “编译失败” | 语法错误或逻辑错误 | 检查代码并修正 |

| “无法启动仿真” | 未安装 ModelSim 或未设置仿真器 | 安装 ModelSim 并配置 |

.v 或 .vhd,不要使用 .hdl。如果你能提供具体的错误信息(比如截图或文字描述),我可以进一步帮你定位问题。

希望这些信息对你有帮助!如果还有其他问题,欢迎继续提问。