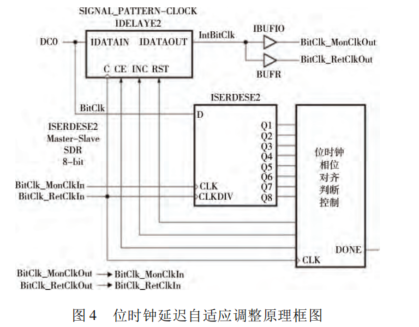

我完全按照了《一种基于片同步技术的高速ADC与FPGA互连方法_韩琦》论文中的这个原理框图

写的代码,逻辑仿真没问题,可是vivado在inplementation实现的时候有一个DRC的电路警告,显示的是IDELAYE2这个延时器的输入信号和输出信号的布线未完成(unrouted),警告如下:1 net(s) are unrouted. The problem bus(es) and/or net(s) are adc_inst/BitClk_Adaptive_Adjustment_inst/bitclk_delay.;;1 net(s) are partially routed. The problem bus(es) and/or net(s) are adc_inst/BitClk_Adaptive_Adjustment_inst/BitClk.;;查阅各种相关资料也没法解决,不知道是什么原因,

IDELAYE2 IDELAYE2_bitclk_inst(.DATAOUT( bitclk_delay ), .C( BitClk_div4 ), .IDATAIN( BitClk), );

IBUFDS IBUFDS_DCO_432M_inst ( .O(BitClk), .I(DCO_p), .IB(DCO_n) );

BUFR #( .BUFR_DIVIDE("4"),.SIM_DEVICE("7SERIES") ) BUFR_inst (.O(BitClk_div4), .CE(1'b1), .CLR(1'b0), .I(bitclk_delay) );

BUFIO bitclk_inst (.O(BitClkout),.I(bitclk_delay) );