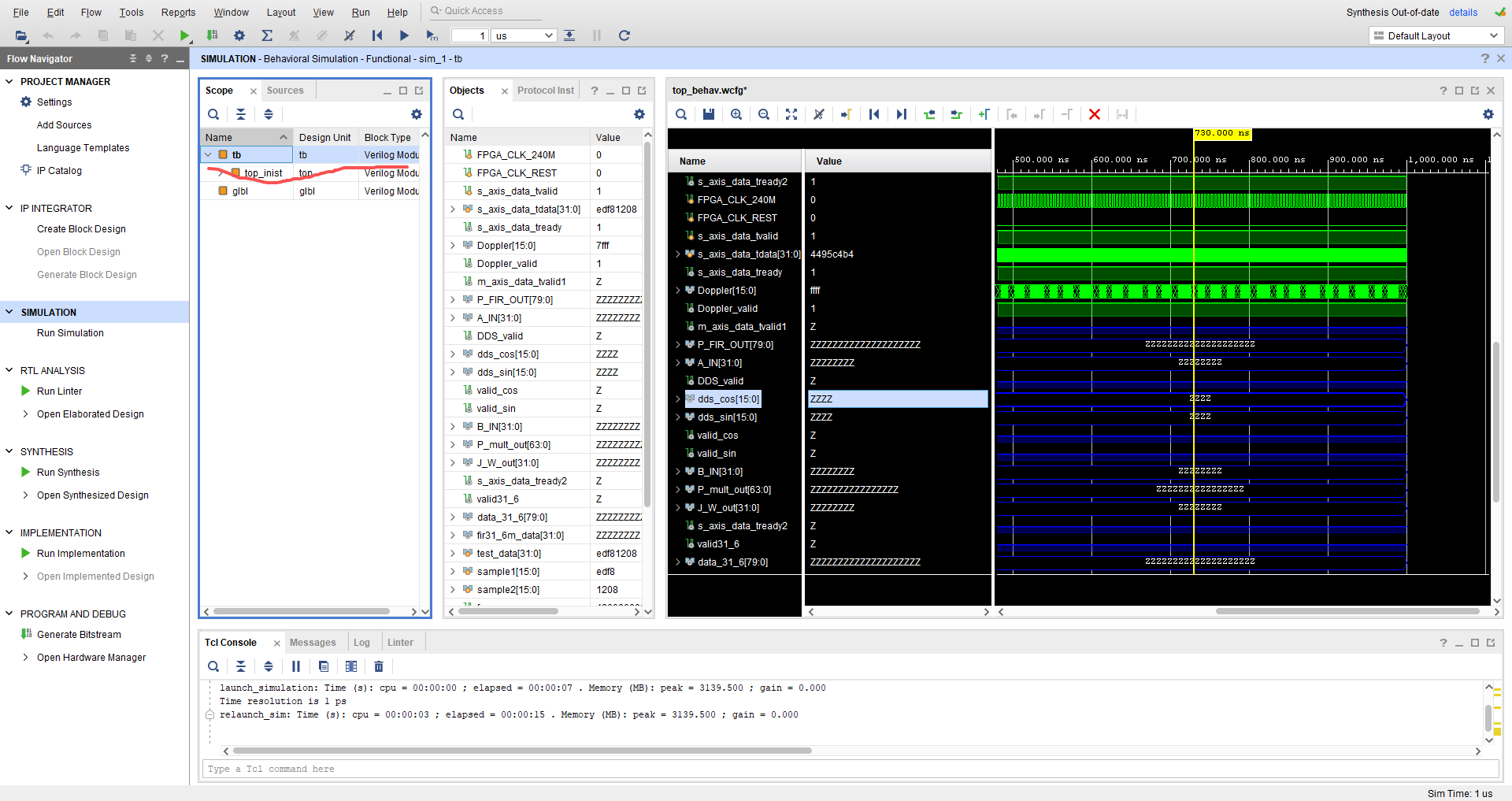

如图,选tb时呈现这样的

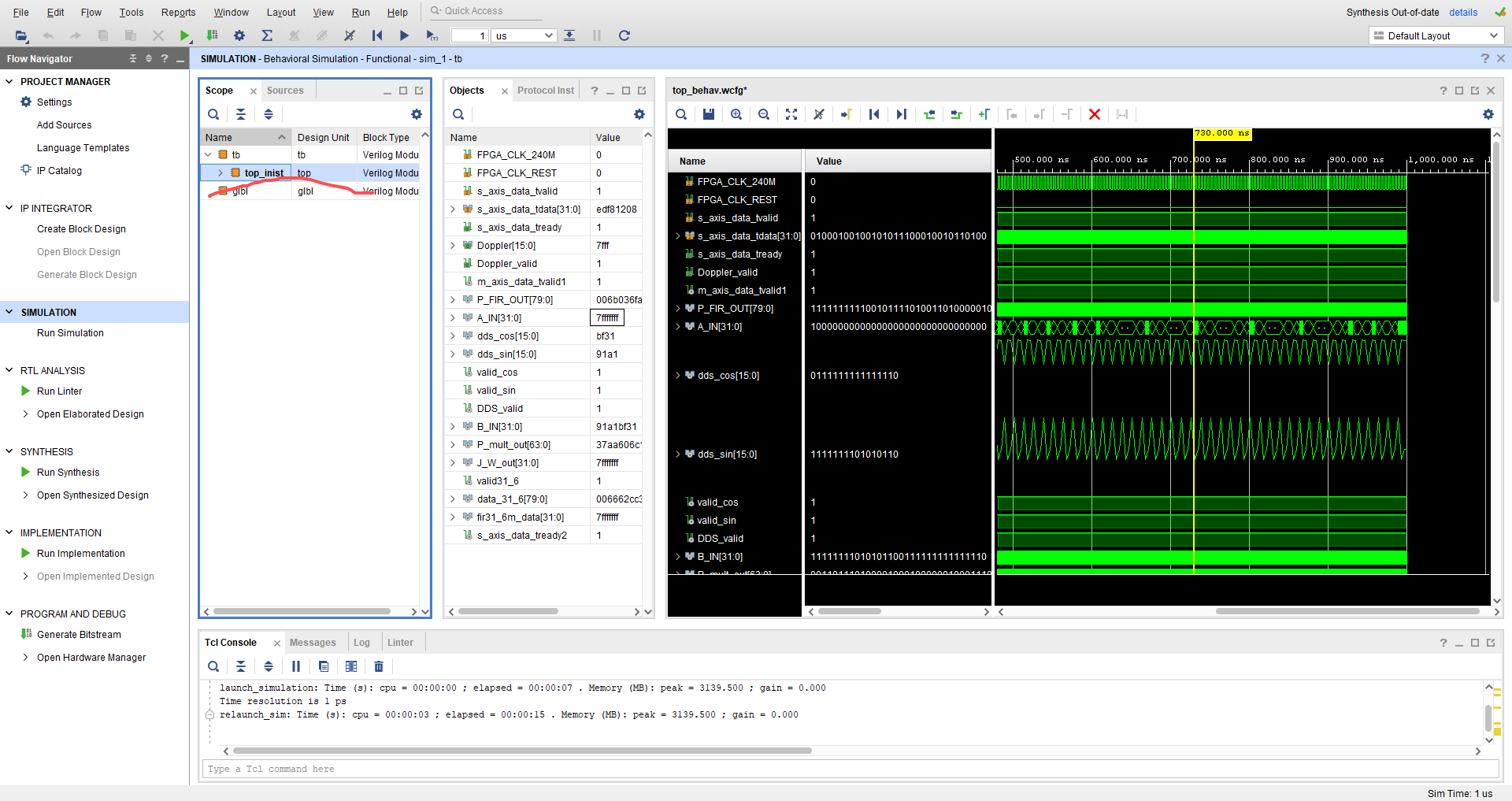

而选择tb下的top.inist模块则正常

下午好🌅🌅🌅

本答案参考通义千问

根据你描述的问题,“Vivado仿真数据呈现高阻态(High-Z)”,并且“选择 tb 时呈现这样的问题,而选择 tb 下的 top.inist 模块则正常”,这通常意味着 测试平台(Testbench, tb)中对某些信号未正确驱动,或者 模块实例化时未正确连接信号。

在数字电路中,高阻态表示一个引脚没有被明确驱动为逻辑 0 或 1,处于一种“悬浮”状态。这种状态可能是因为:

以下是几种常见原因:

initial 或 always 块对信号进行初始化确保所有的输入信号都已被驱动,包括时钟、复位、控制信号等。

// 示例:测试平台中驱动信号

module tb;

reg clk;

reg rst_n;

wire [7:0] data_out;

// 实例化顶层模块

top u_top (

.clk(clk),

.rst_n(rst_n),

.data_out(data_out)

);

initial begin

clk = 0;

rst_n = 0;

#10 rst_n = 1; // 复位释放

#100 $finish; // 仿真结束

end

always #5 clk = ~clk; // 时钟生成

endmodule

如果 data_out 是输出信号,且未被驱动,就会出现高阻态。

检查 top 模块是否正确地将信号传递到 inist 模块。

// top.v

module top (

input clk,

input rst_n,

output reg [7:0] data_out

);

// 实例化 inist 模块

inist u_inist (

.clk(clk),

.rst_n(rst_n),

.data_out(data_out)

);

endmodule

如果

inist模块中的data_out是一个 wire 类型,则不能用reg连接,会导致高阻态。

wire 和 reg 的区别:

reg 用于可赋值的信号(如寄存器)wire 用于连续赋值或模块输出// inist.v

module inist (

input clk,

input rst_n,

output wire [7:0] data_out

);

// 例如:通过组合逻辑驱动 data_out

assign data_out = ...;

endmodule

如果

data_out是wire,但你在top中用reg连接,会导致错误。

initial 或 always 初始化信号确保所有信号在仿真开始前有默认值。

initial begin

clk = 0;

rst_n = 0;

data_out = 8'b0;

end

在 Vivado 中,确保选择了正确的测试平台(tb),并运行了仿真。

tb 模块 → 选择 Simulate Behavioral Model如果你的 top 模块中引用了 inist 模块,但 inist 的输出是 wire,而你却在 top 中将其声明为 reg,请修改如下:

module top (

input clk,

input rst_n,

output reg [7:0] data_out // 错误!应为 wire

);

inist u_inist (

.clk(clk),

.rst_n(rst_n),

.data_out(data_out) // 若 inist 的 data_out 是 wire,这里会出错

);

endmodule

module top (

input clk,

input rst_n,

output wire [7:0] data_out // 正确!与 inist 的 wire 类型一致

);

inist u_inist (

.clk(clk),

.rst_n(rst_n),

.data_out(data_out)

);

endmodule

| 问题 | 解决方案 |

|------|----------|

| 高阻态 | 确保所有信号都被驱动 |

| 模块连接错误 | 检查信号类型和连接方式 |

| 信号类型不匹配 | 确保 reg 和 wire 类型一致 |

| 未初始化 | 使用 initial 或 always 初始化信号 |

| 仿真设置错误 | 确保选择了正确的测试平台 |

如果你能提供具体的代码片段或波形截图,我可以进一步帮助你定位问题。希望这些信息对你有帮助!