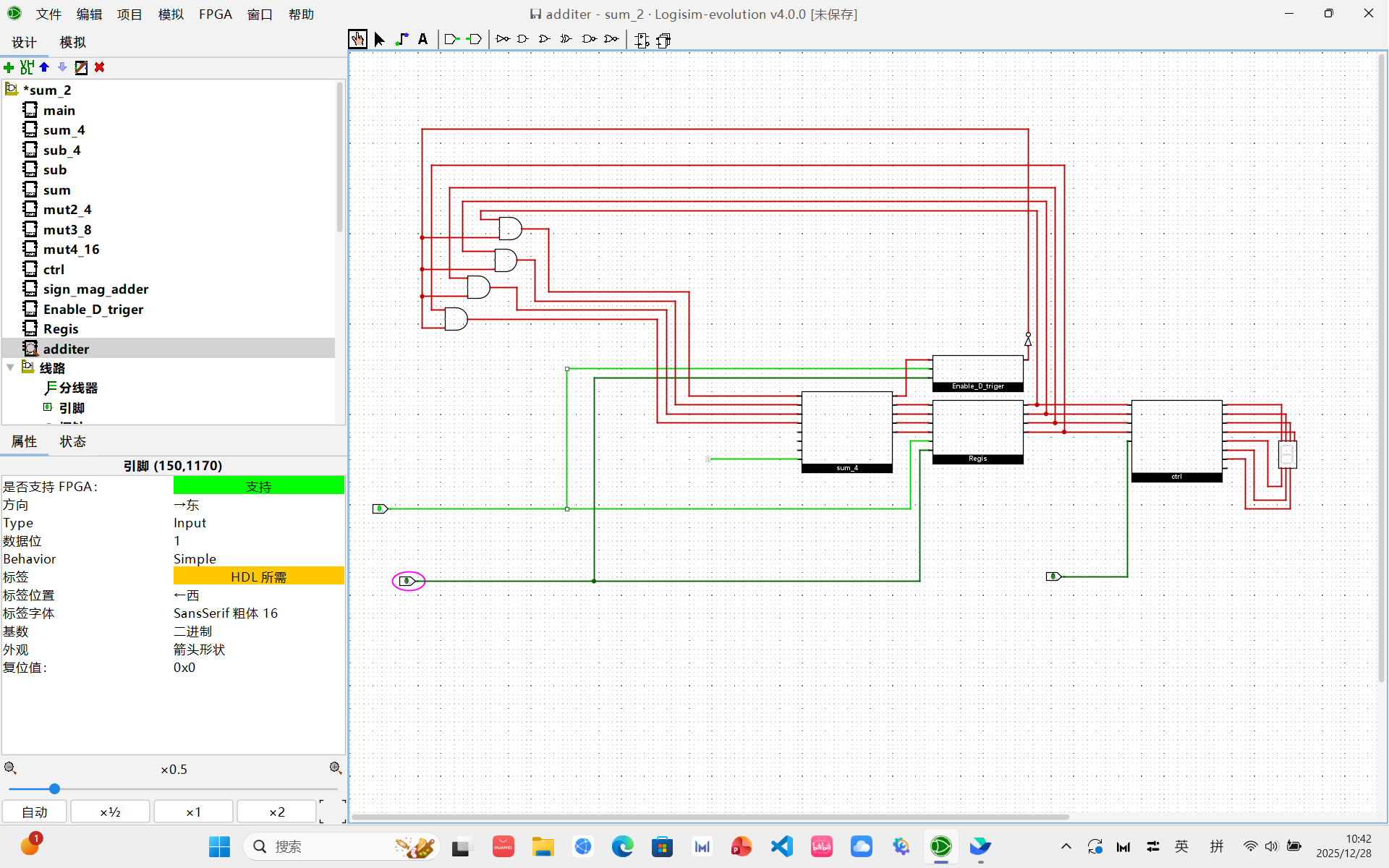

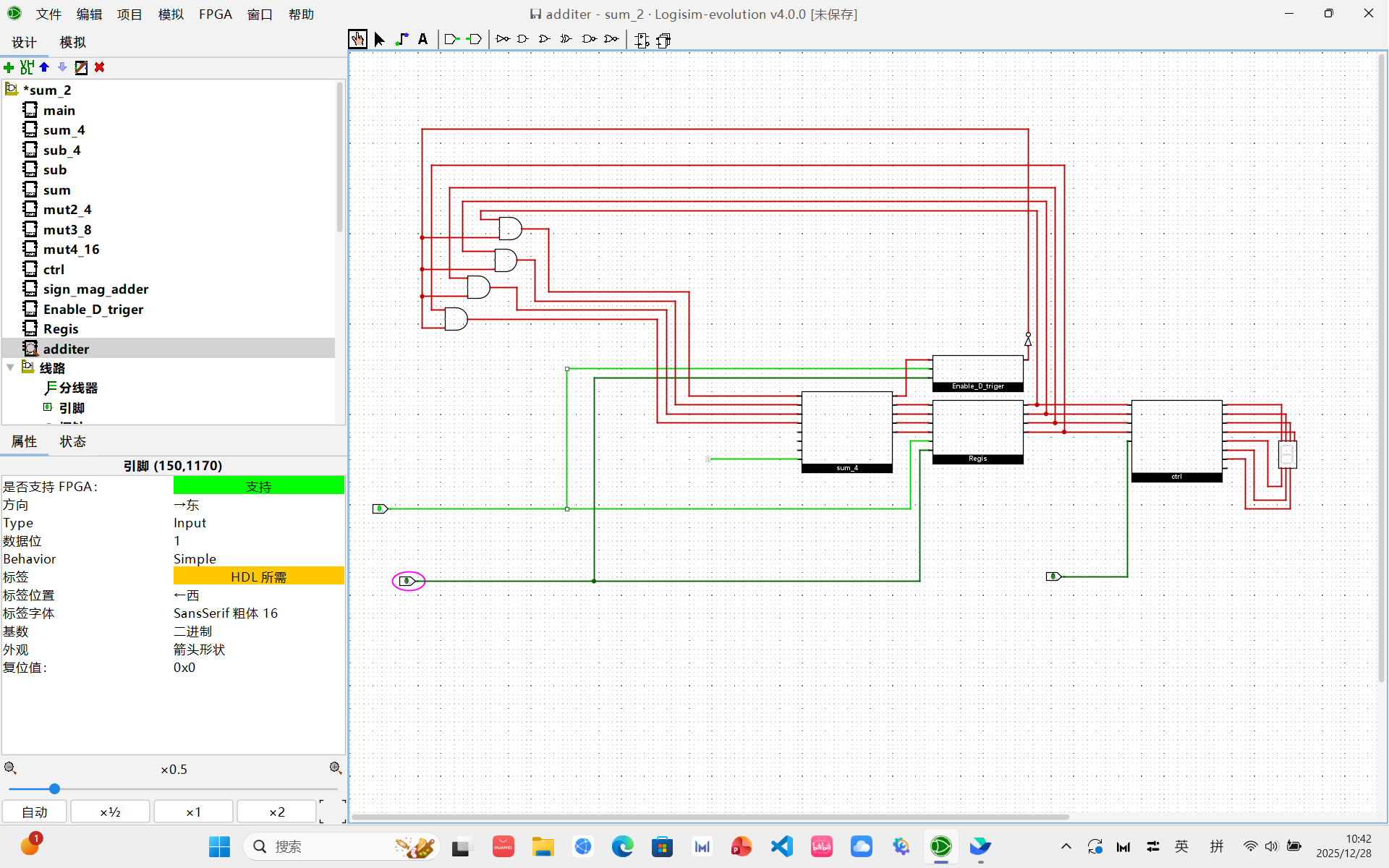

为什么计数器一直是红色的,时钟信号怎么震数据也过不去

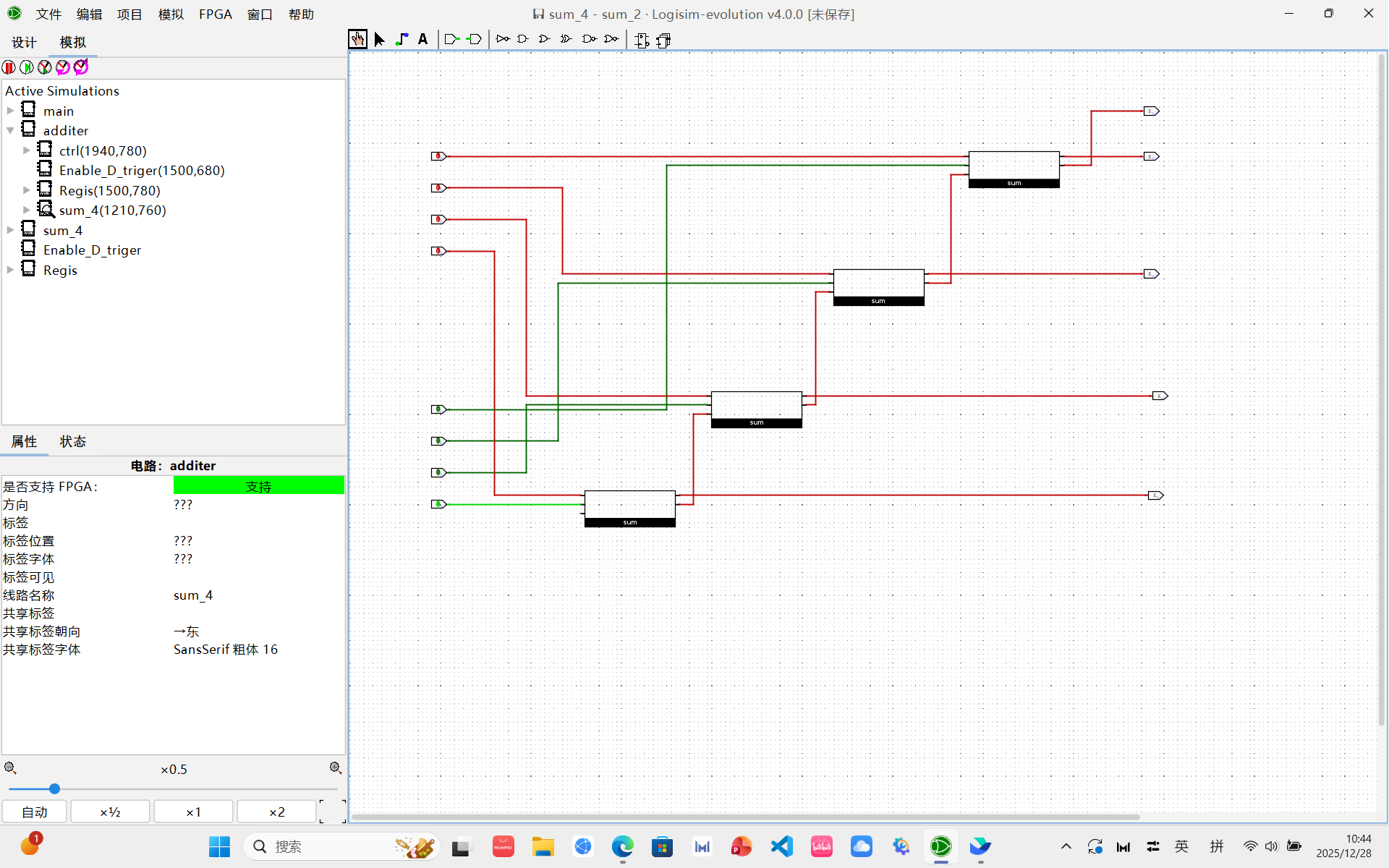

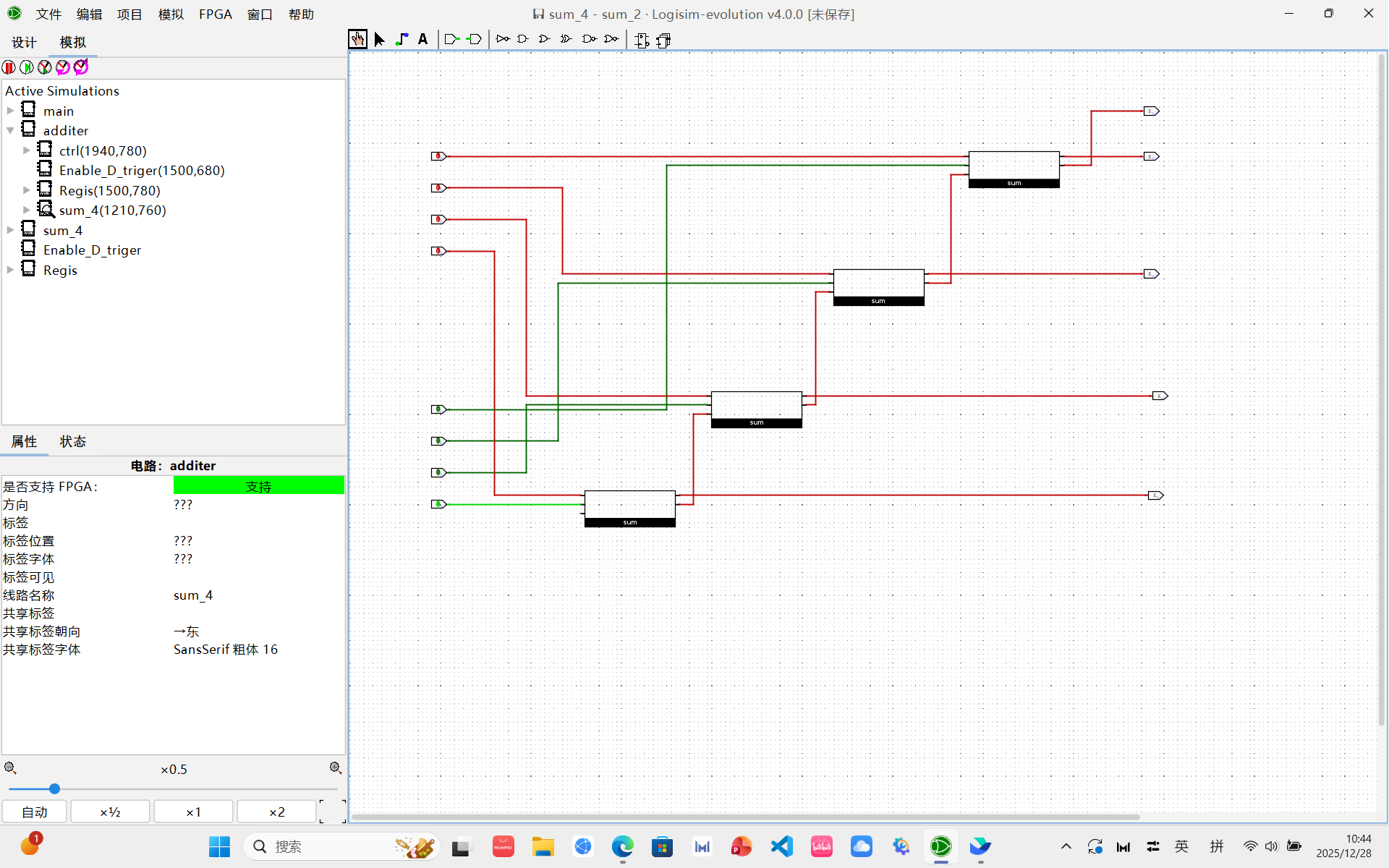

这个是sum_4加法器

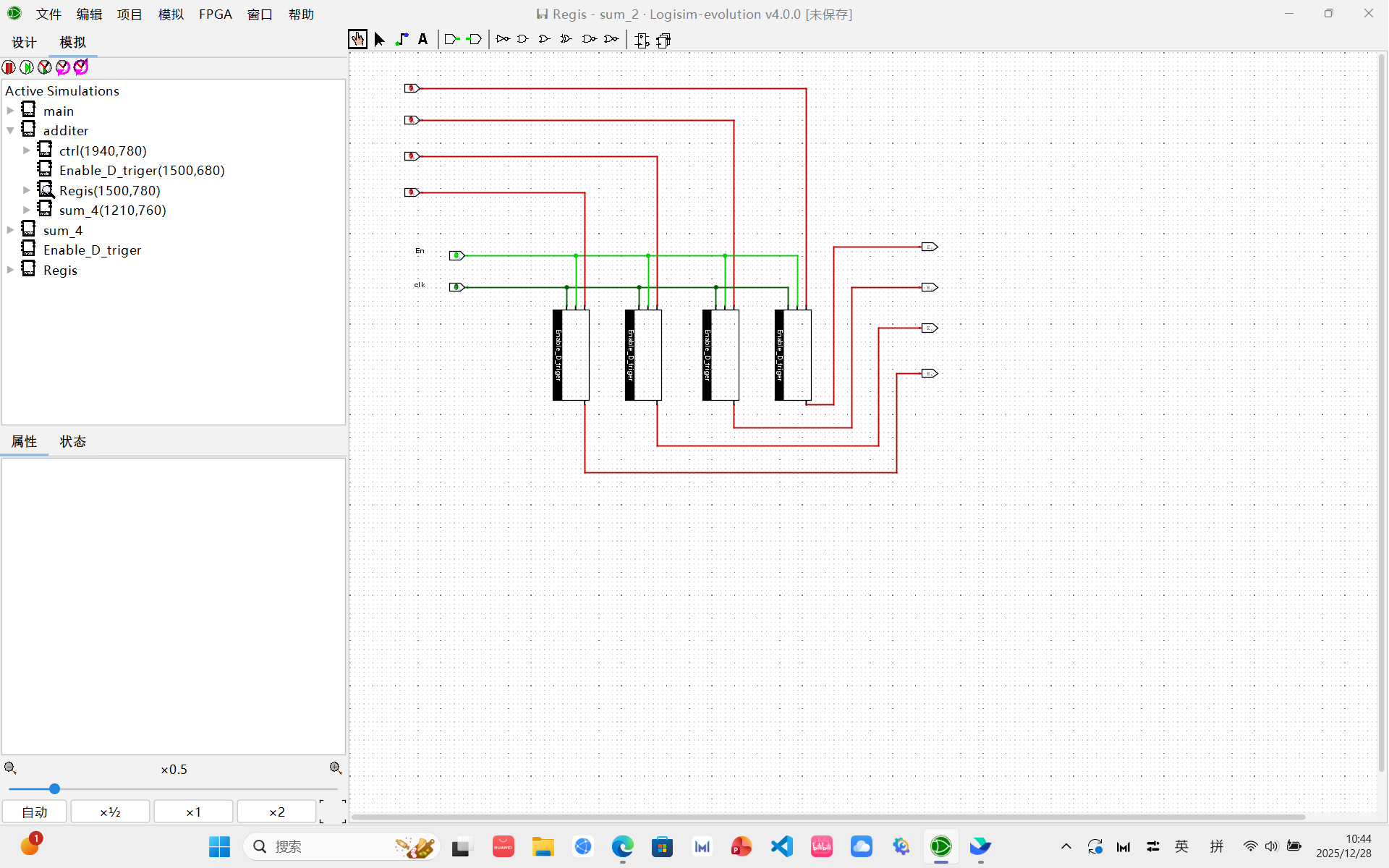

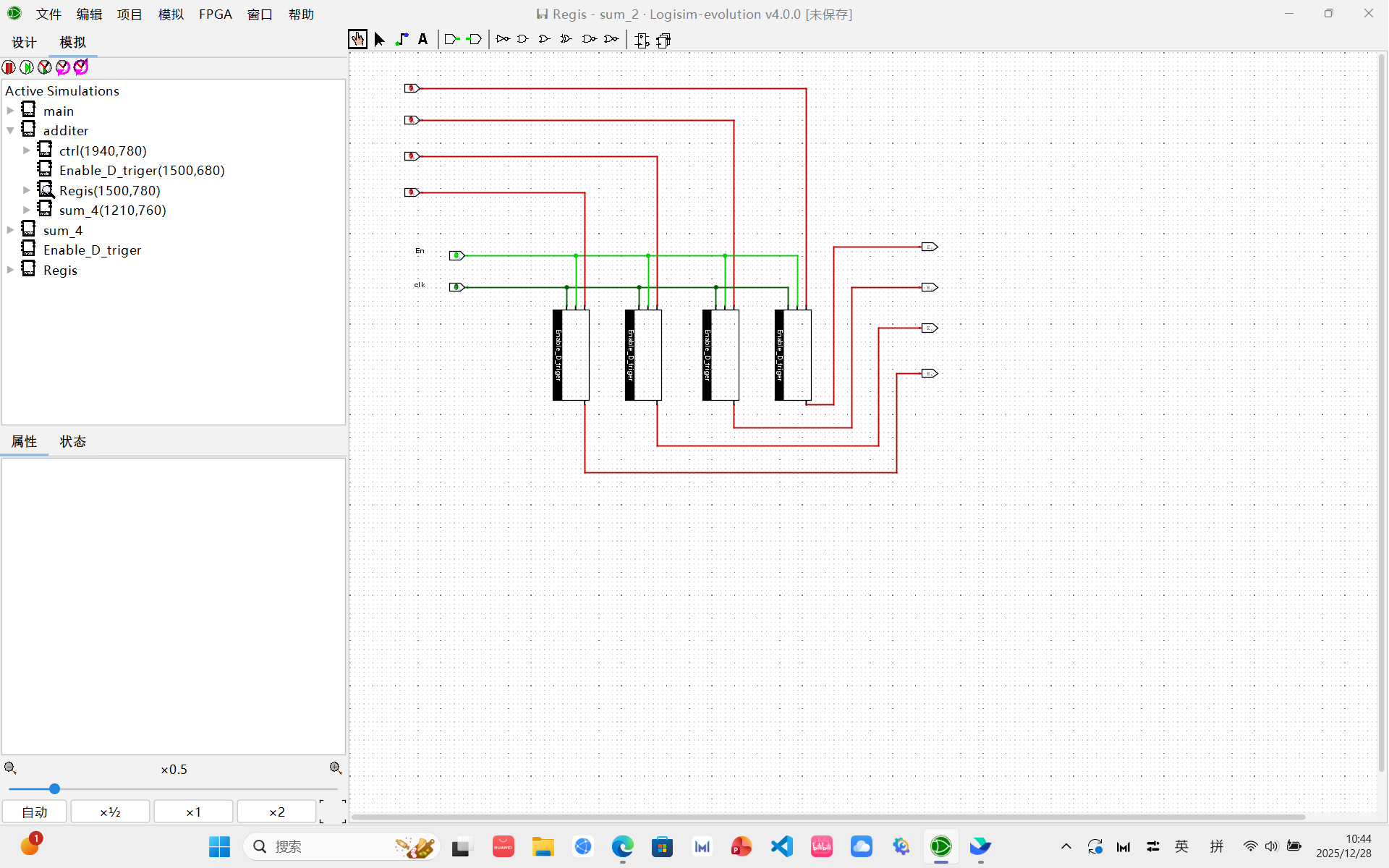

这个是四位寄存器

这个是D触发器

为什么计数器一直是红色的,时钟信号怎么震数据也过不去

阿里嘎多学长整理AIGC生成,因移动端显示问题导致当前答案未能完全显示,请使用PC端查看更加详细的解答过程

问题分析

根据你的描述,问题似乎是关于FPGA开发中的计数器和触发器设计。计数器一直是红色的,可能是因为计数器的值溢出或计数器的信号没有被正确地处理。时钟信号怎么震数据也过不去,可能是因为触发器的设计有问题,导致数据无法被正确地传递。

解决方案

核心代码

library IEEE;

use IEEE.STD_LOGIC;

use IEEE.NUMERIC_STD.ALL;

entity sum_4_adder is

Port ( clk : in STD_LOGIC;

rst : in STD_LOGIC;

data_in : in STD_LOGIC_VECTOR (3 downto 0);

data_out : out STD_LOGIC_VECTOR (3 downto 0));

end sum_4_adder;

architecture Behavioral of sum_4_adder is

signal count : unsigned (3 downto 0) := (others => '0');

begin

process(clk)

begin

if rising_edge(clk) then

if rst = '1' then

count <= (others => '0');

else

count <= count + 1;

end if;

end if;

end process;

data_out <= std_logic_vector(count);

end Behavioral;

上面的代码是一个简单的计数器设计,使用了VHDL语言。计数器的值每次时钟信号上升时加1。数据输出是计数器的值。