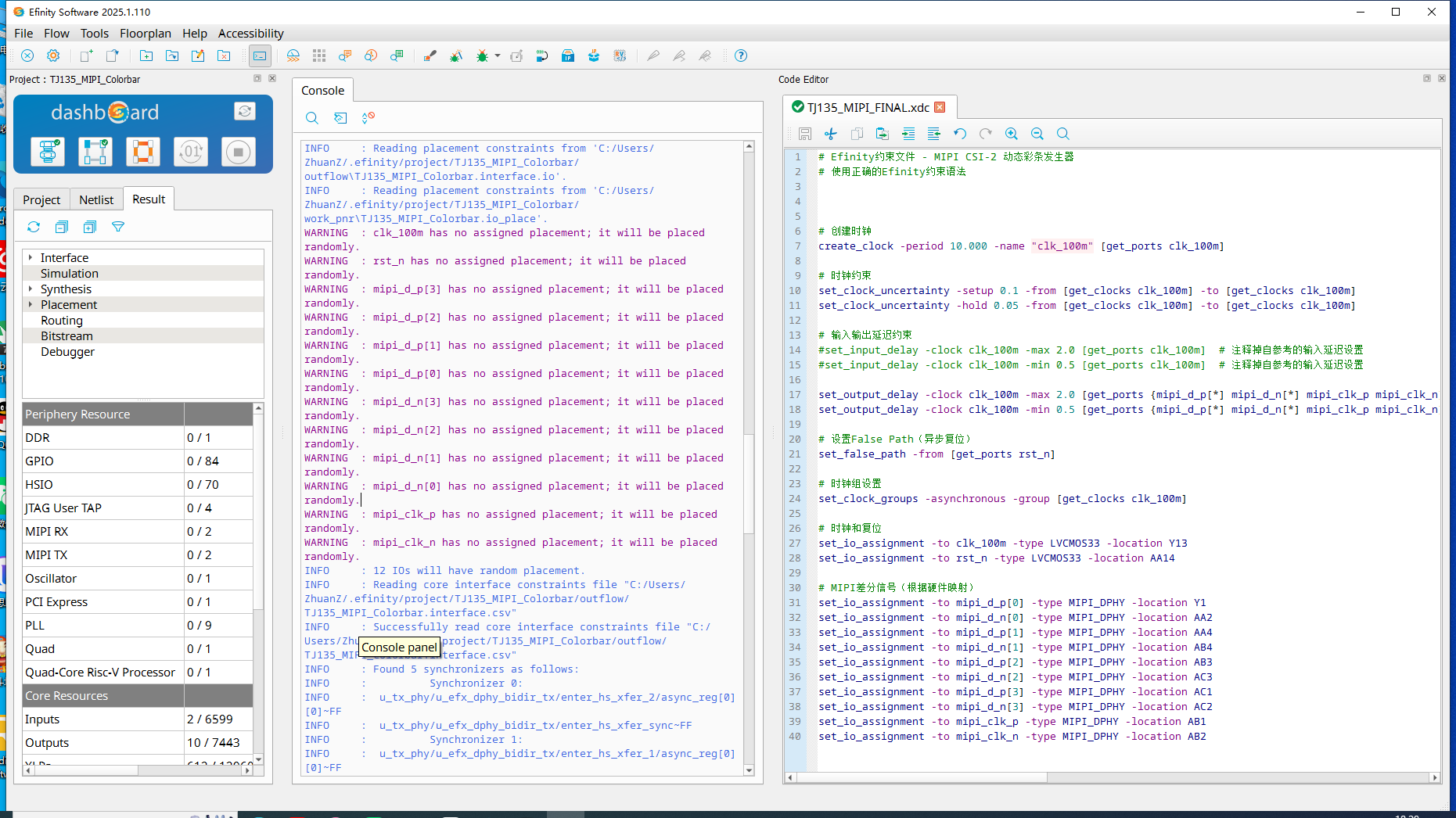

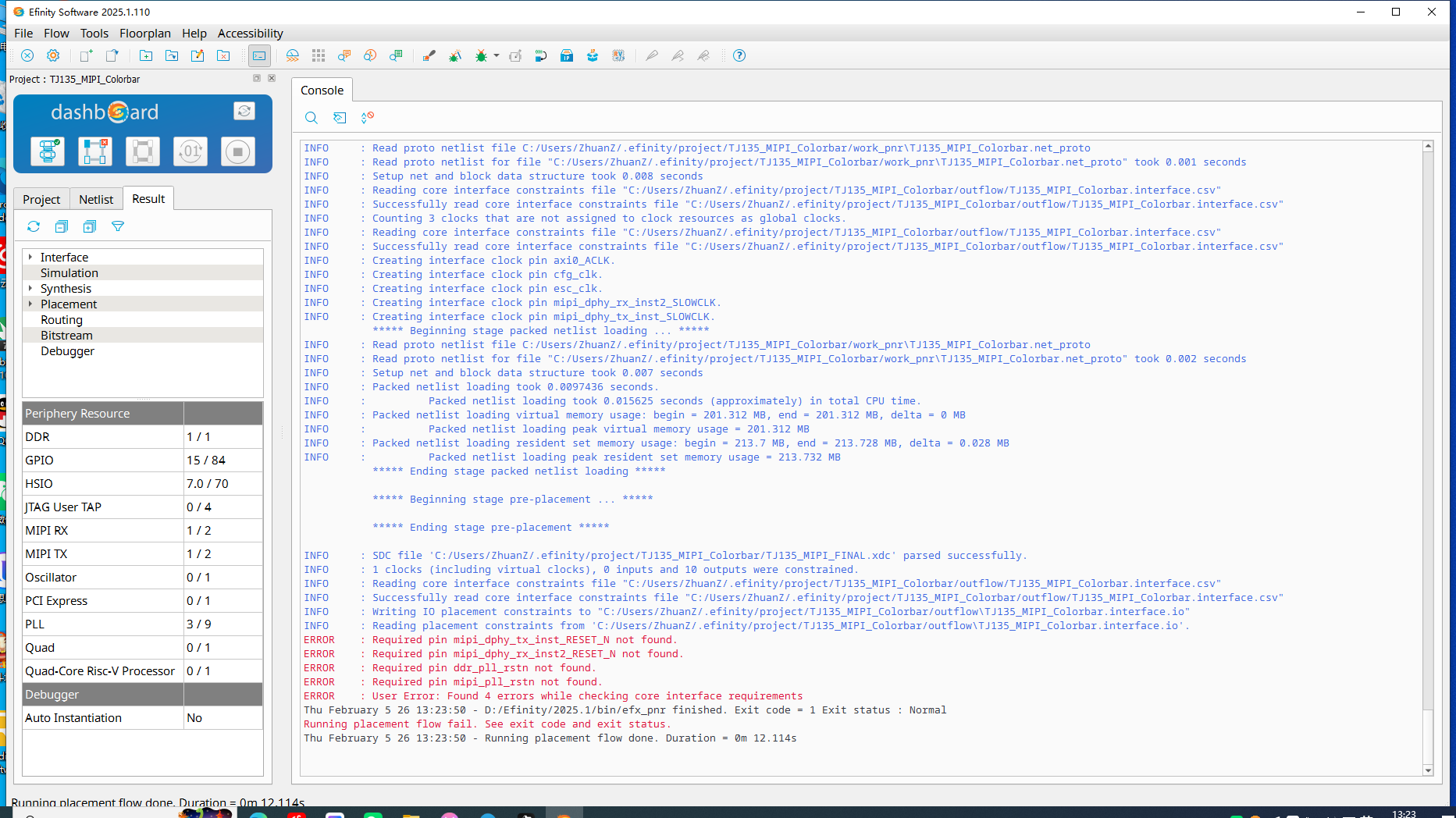

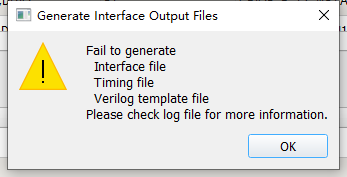

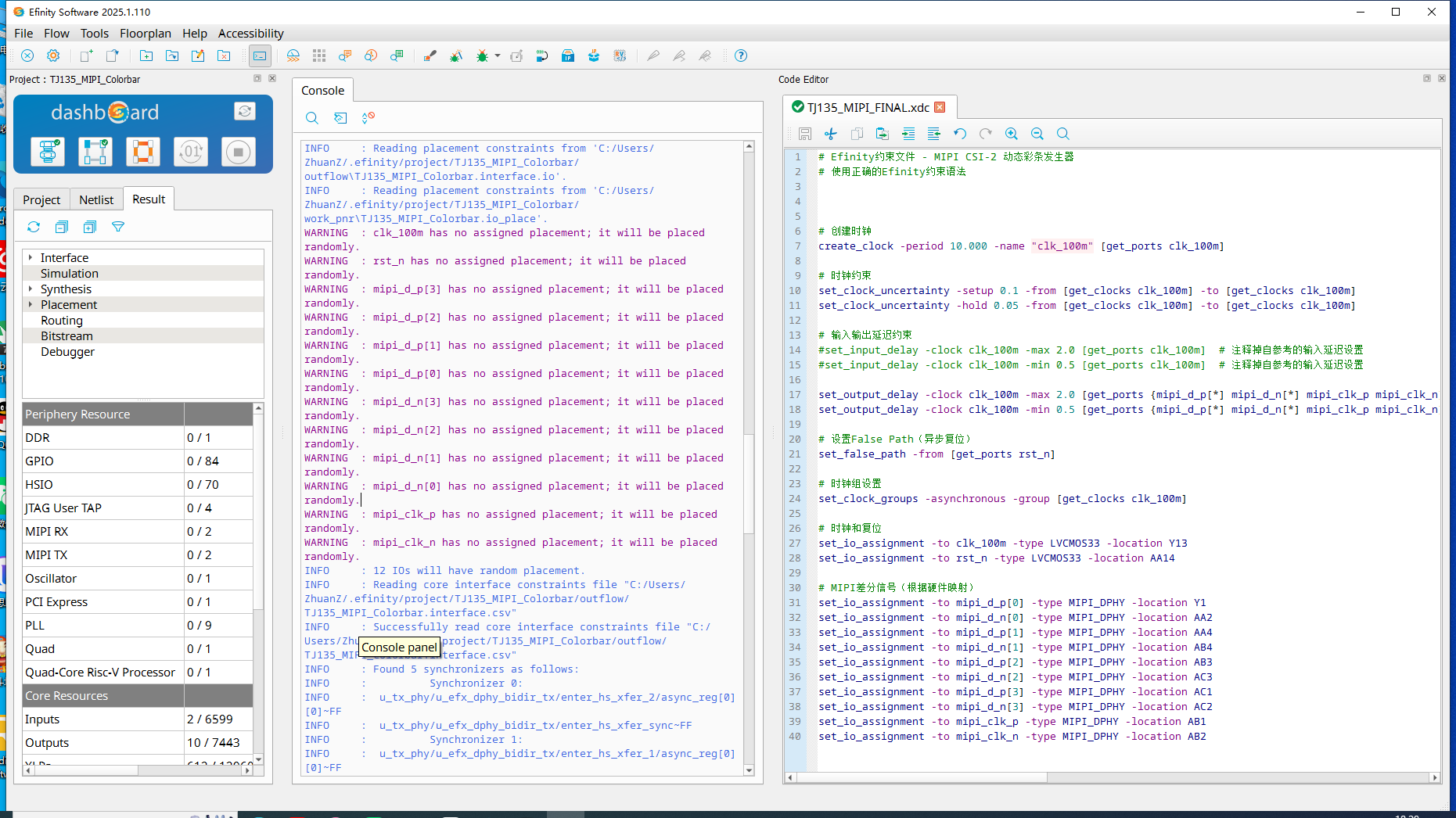

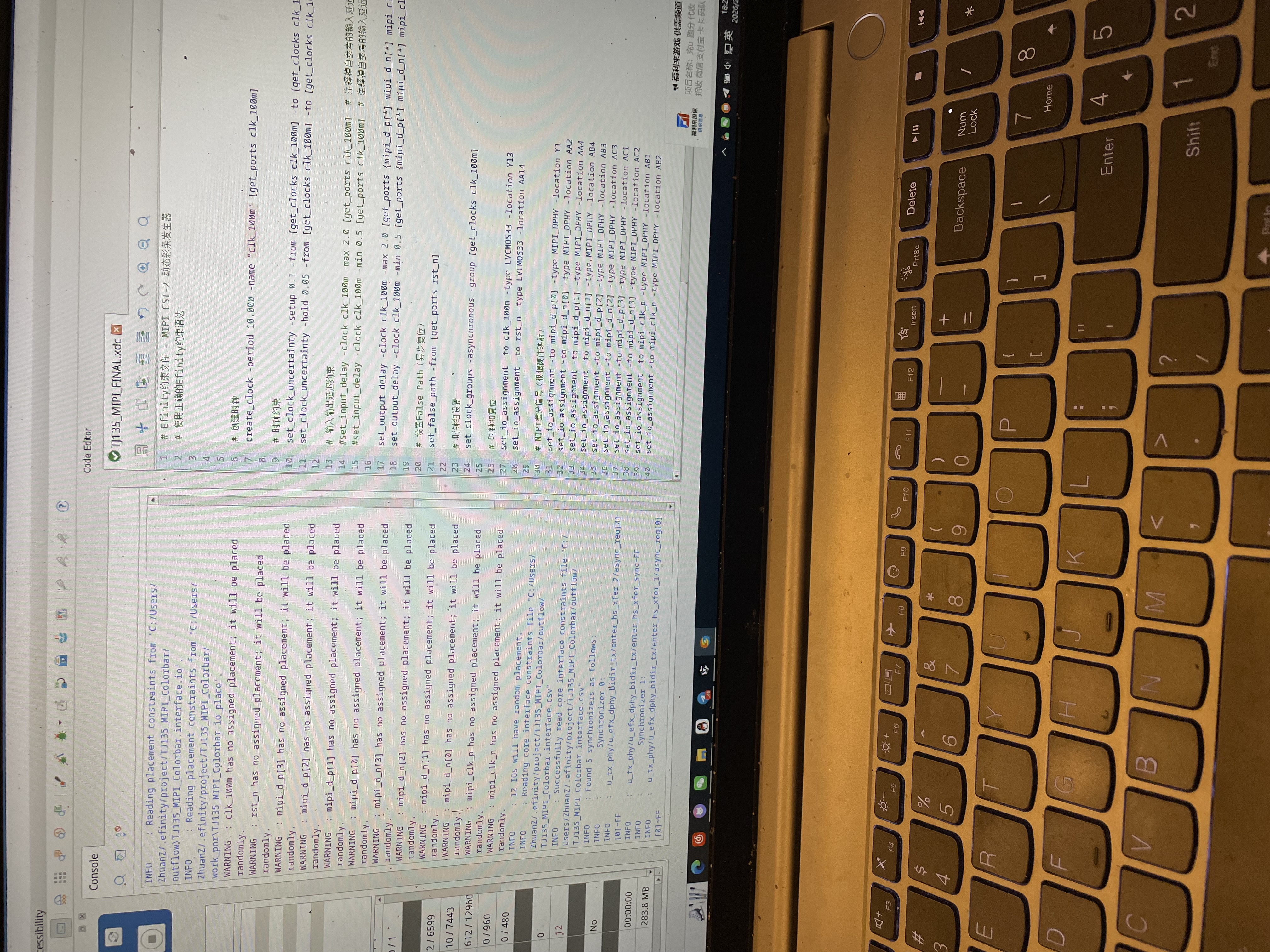

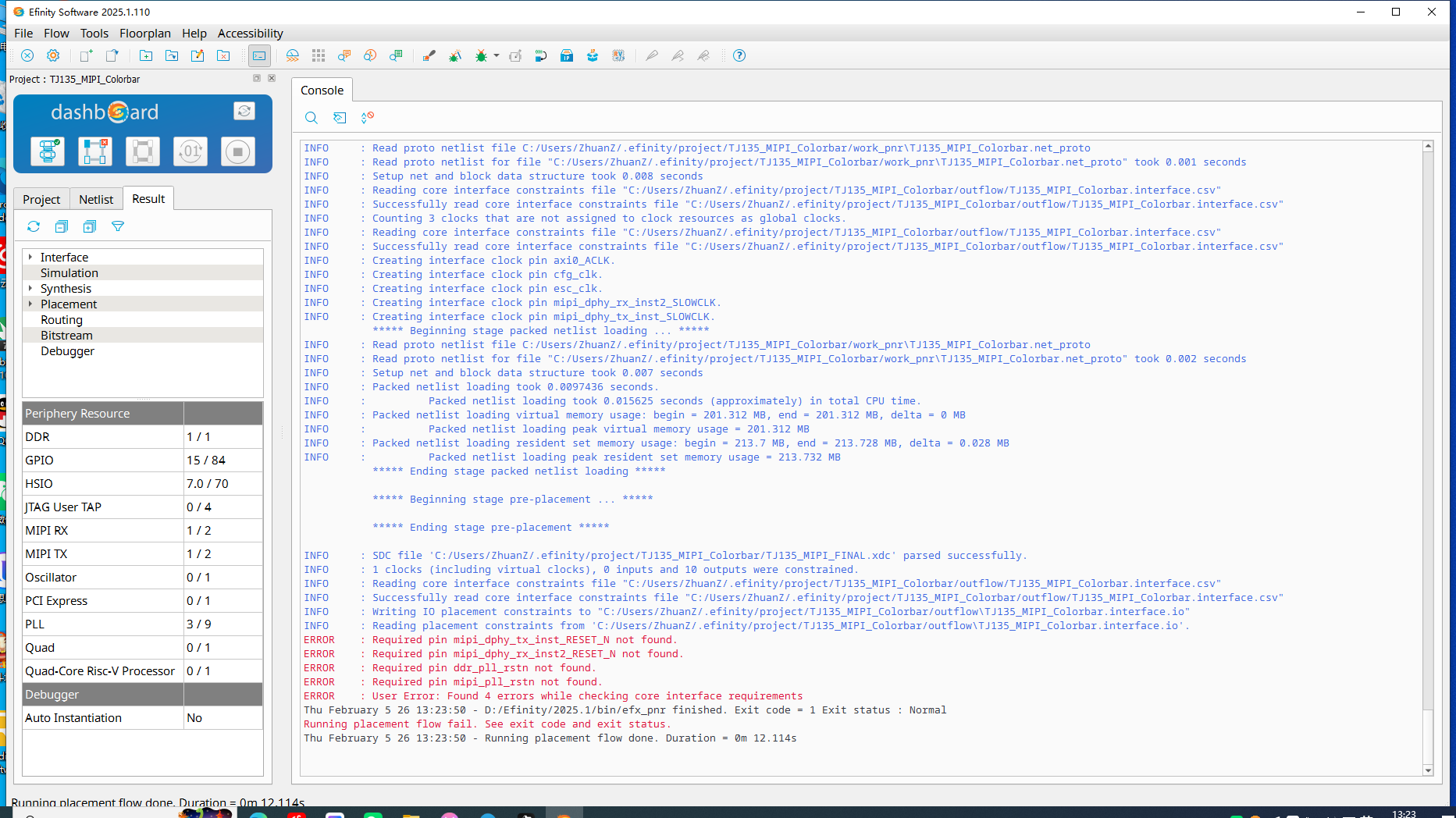

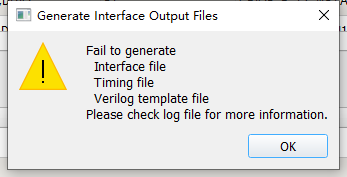

头真的好大 要怎么处理 求引脚解决方法 好心累 ai给的办法没屁用 怎么样解决图片的问题

头真的好大 要怎么处理 求引脚解决方法 好心累 ai给的办法没屁用 怎么样解决图片的问题

晚上好🌙🌙🌙

本答案参考通义千问

你提到的“易灵思FPGA引脚问题”是一个在硬件开发中非常常见的问题,尤其是对于刚接触FPGA开发的新手来说,可能会遇到很多关于引脚分配、约束文件(.xdc)配置、信号冲突、时序问题、电源和地引脚设置等难题。下面我将从多个角度详细分析并提供解决方案。

你提到“磨了我好几天了 真的好难受啊_硬件开发”,说明你可能遇到了以下几类问题之一:

重点:引脚分配必须基于具体的FPGA型号和开发板型号进行。

# 正确示例:为一个LED分配引脚

set_property -dict {PACKAGE_PIN J17 IOSTANDARD LVCMOS33} [get_ports LED]

# 错误:引脚J17已经被分配给其他信号

set_property -dict {PACKAGE_PIN J17 IOSTANDARD LVCMOS33} [get_ports LED]

set_property -dict {PACKAGE_PIN J17 IOSTANDARD LVCMOS33} [get_ports BTN] # 冲突!

重点:确保每个引脚只被一个信号使用,并且引脚类型与逻辑一致。

如果你是新手,可以使用 Vivado、Lattice Diamond、iCEcube2 等工具的 自动引脚分配功能。

重点:自动分配能大大减少人为错误,但最终仍需验证是否符合实际硬件要求。

set_property -dict {PACKAGE_PIN A1 IOSTANDARD GND} [get_ports VCC]

set_property -dict {PACKAGE_PIN B1 IOSTANDARD GND} [get_ports GND]

重点:不要忽略电源和地引脚的配置,这是FPGA正常工作的基础。

重点:引脚冲突是常见问题,一定要仔细排查。

你说“怎么样解决图片的问题”,可能是以下几种情况:

重点:如果图片无法加载,可能是路径错误或格式不支持,需要重新准备或转换。

# 正确的引脚分配示例

set_property -dict {PACKAGE_PIN J17 IOSTANDARD LVCMOS33} [get_ports LED]

set_property -dict {PACKAGE_PIN K17 IOSTANDARD LVCMOS33} [get_ports BTN]

set_property -dict {PACKAGE_PIN A1 IOSTANDARD GND} [get_ports GND]

set_property -dict {PACKAGE_PIN B1 IOSTANDARD VCC} [get_ports VCC]

如果你愿意,可以贴出你的 约束文件(.xdc) 或 错误提示截图,我可以帮你具体分析问题所在。希望你能早日解决这个问题,不再烦恼 😊