晚上好🌙🌙🌙

本答案参考通义千问

你提到“工程可以运行成功,位流也可以正常下载,输出,上机就是识别不了PCIe设备”,这说明你的设计在逻辑层面没有问题,但实际硬件上无法识别PCIe设备。这种问题通常涉及硬件配置、驱动、固件或接口连接等多个方面。以下是一些可能的原因及详细解决方案:

一、硬件连接与物理层问题

1. PCIe插槽或设备未正确连接

- 原因:PCIe卡未正确插入主板的PCIe插槽,或者插槽本身有故障。

- 解决方法:

- 检查PCIe卡是否完全插入到主板的对应插槽中。

- 尝试更换其他PCIe插槽或使用其他PCIe设备测试。

- 使用万用表检查插槽是否有电压或短路现象。

2. 电源供电不足

- 原因:PCIe设备需要额外的电源支持(如显卡、网卡等),如果电源功率不足,可能导致设备无法被识别。

- 解决方法:

- 确保电源满足PCIe设备的功耗需求。

- 更换更高功率的电源模块。

3. PCIe版本不匹配

- 原因:主板和PCIe设备的版本不一致(如PCIe 3.0 vs PCIe 4.0)。

- 解决方法:

- 查看主板手册确认支持的PCIe版本。

- 如果设备兼容,尝试在BIOS中设置为兼容模式。

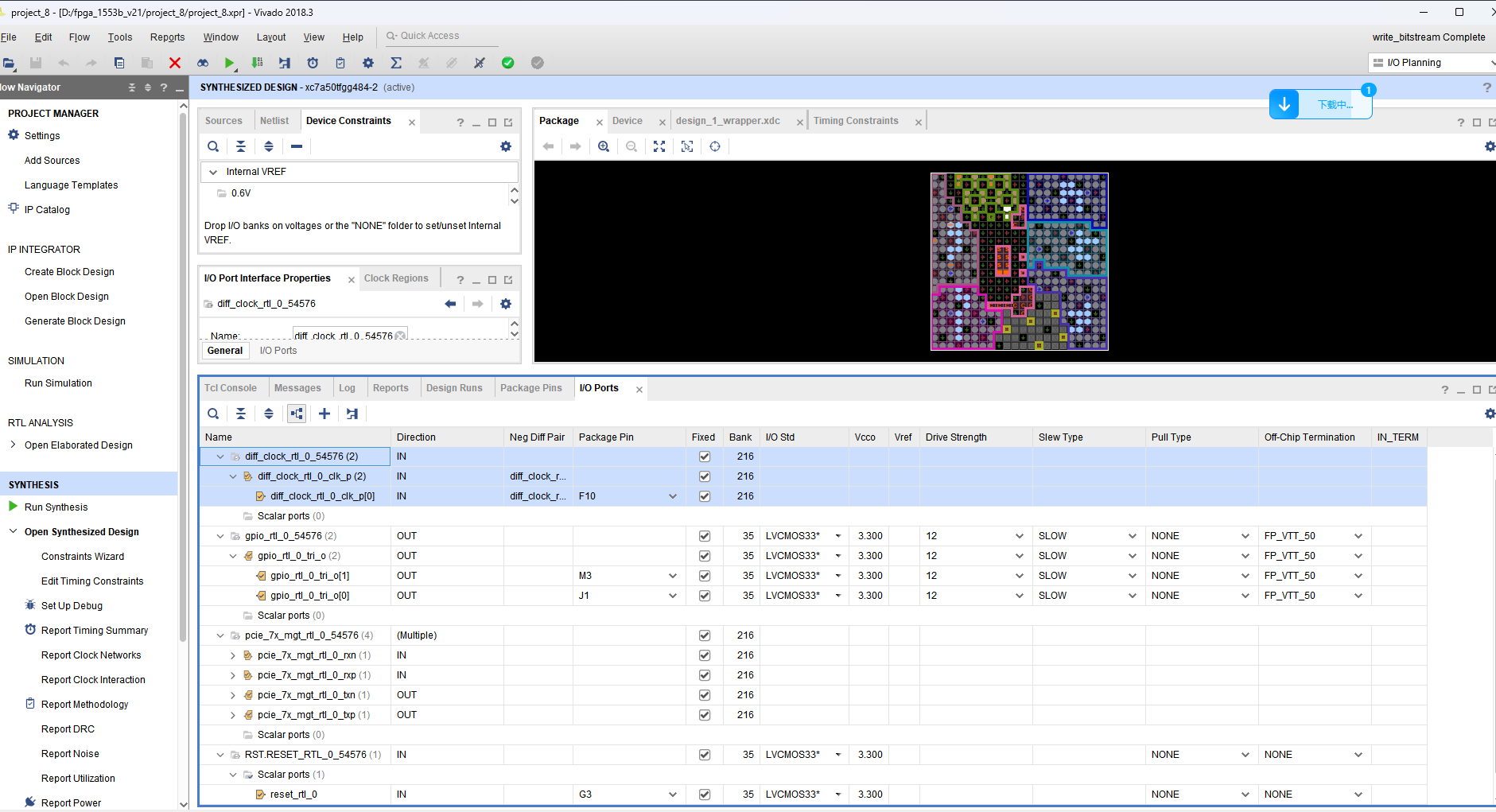

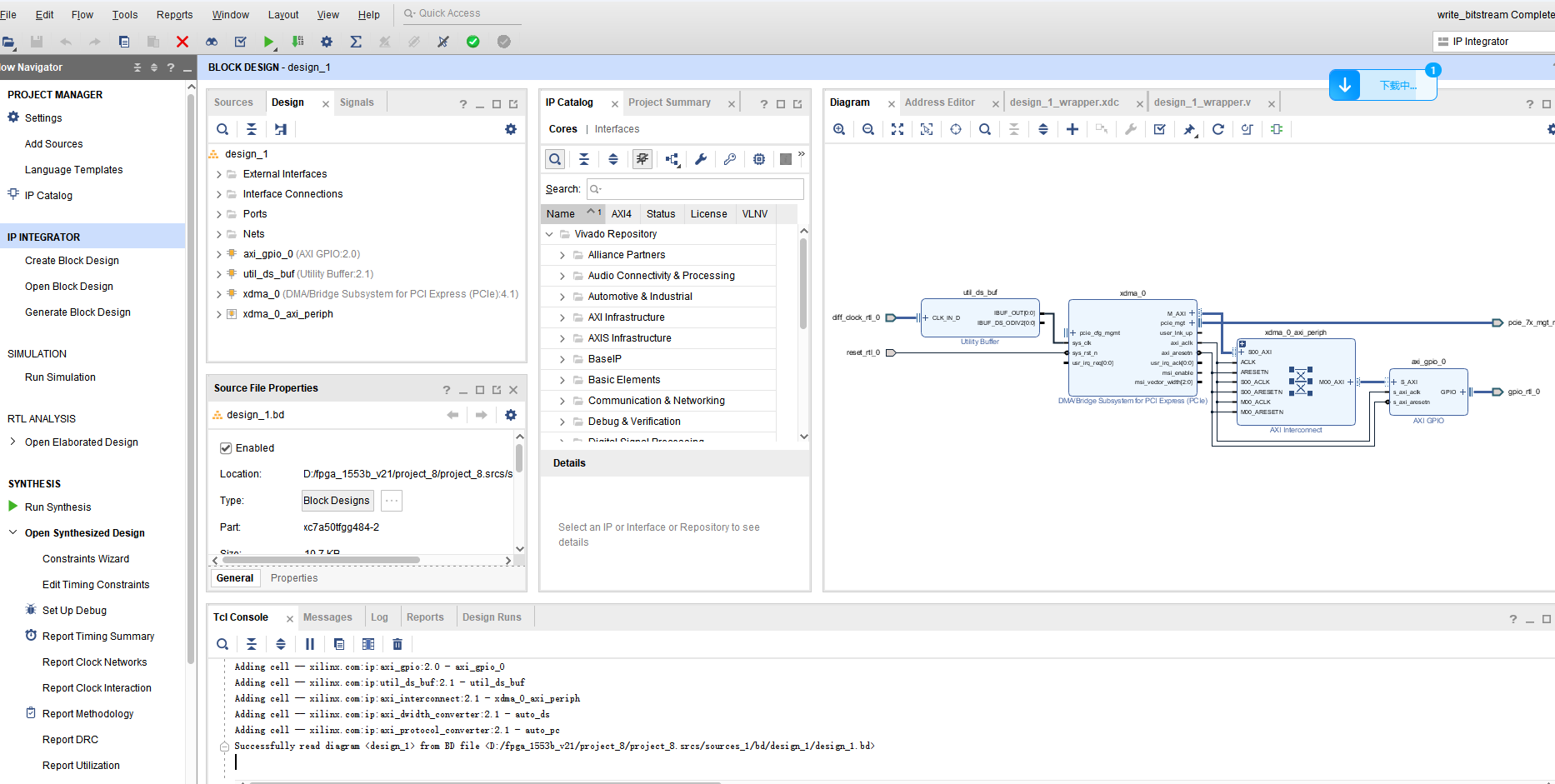

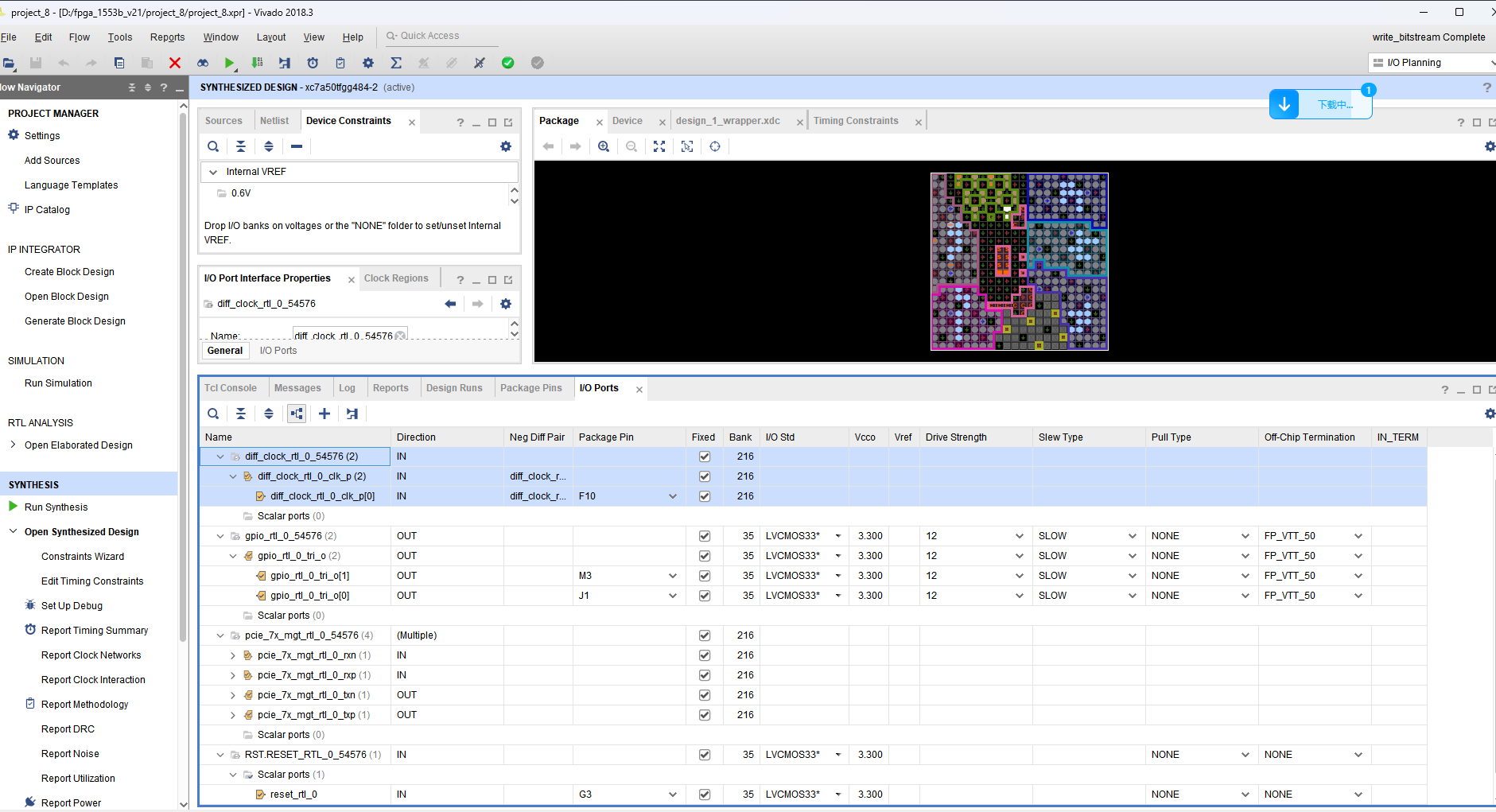

二、FPGA开发相关问题

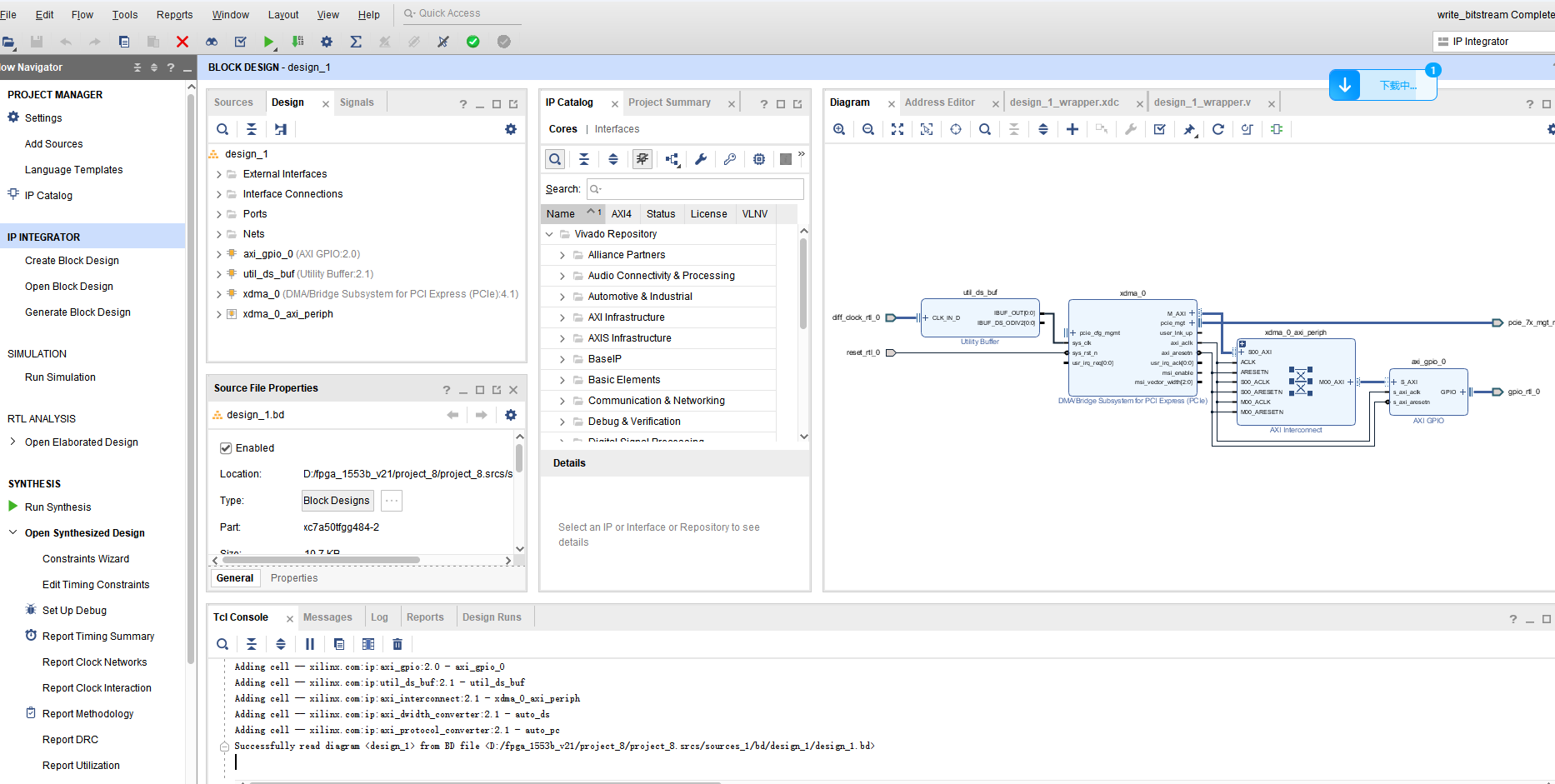

1. PCIe IP核配置错误

- 原因:在FPGA开发中,如果PCIe IP核配置不当(如地址映射、中断设置、数据宽度等),可能导致设备无法被识别。

- 解决方法:

- 检查Xilinx或Intel的PCIe IP核配置是否正确。

- 确认IP核的地址空间分配是否合理,是否与主机端驱动程序匹配。

- 建议使用官方提供的示例工程进行对比调试。

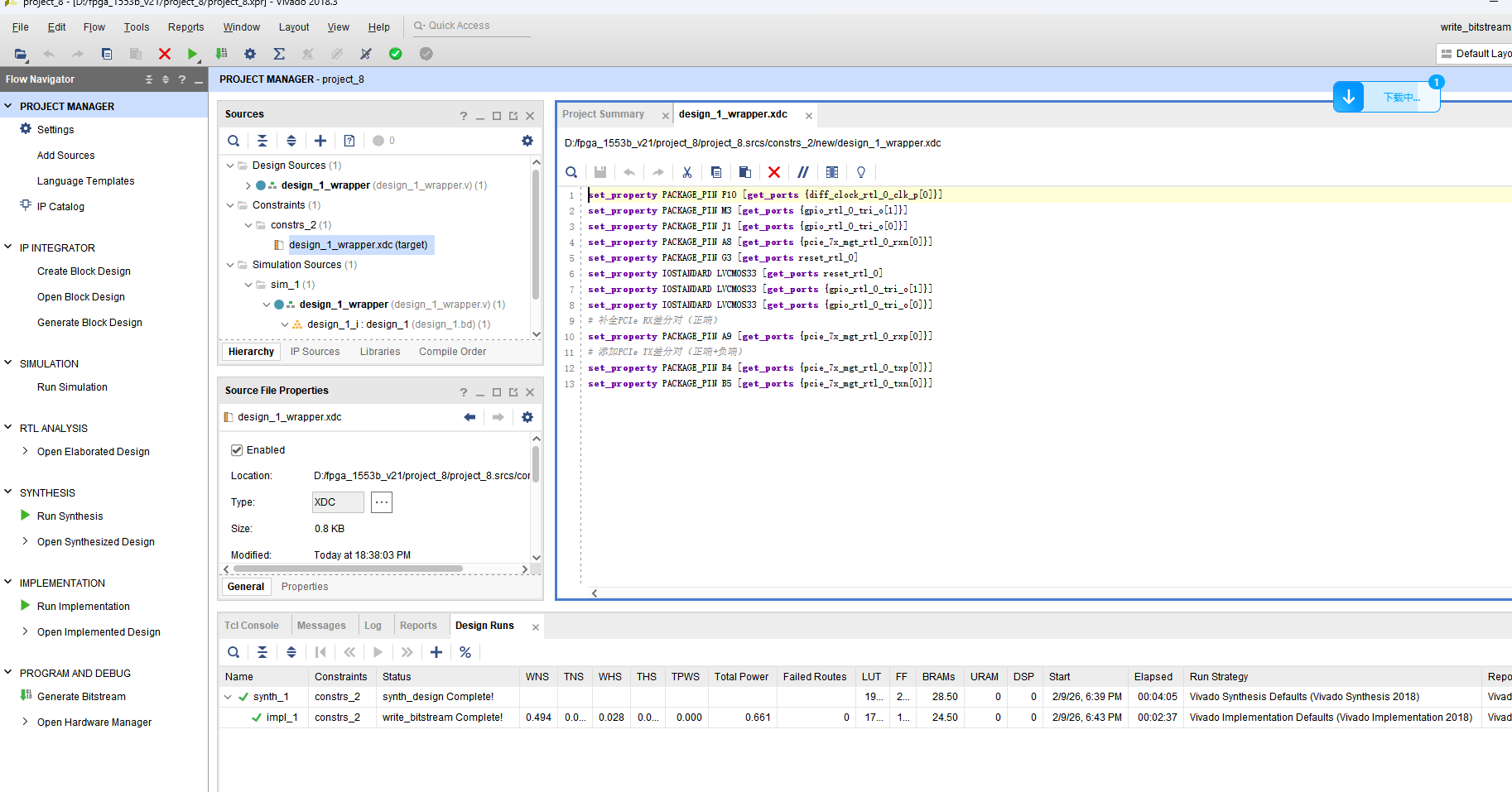

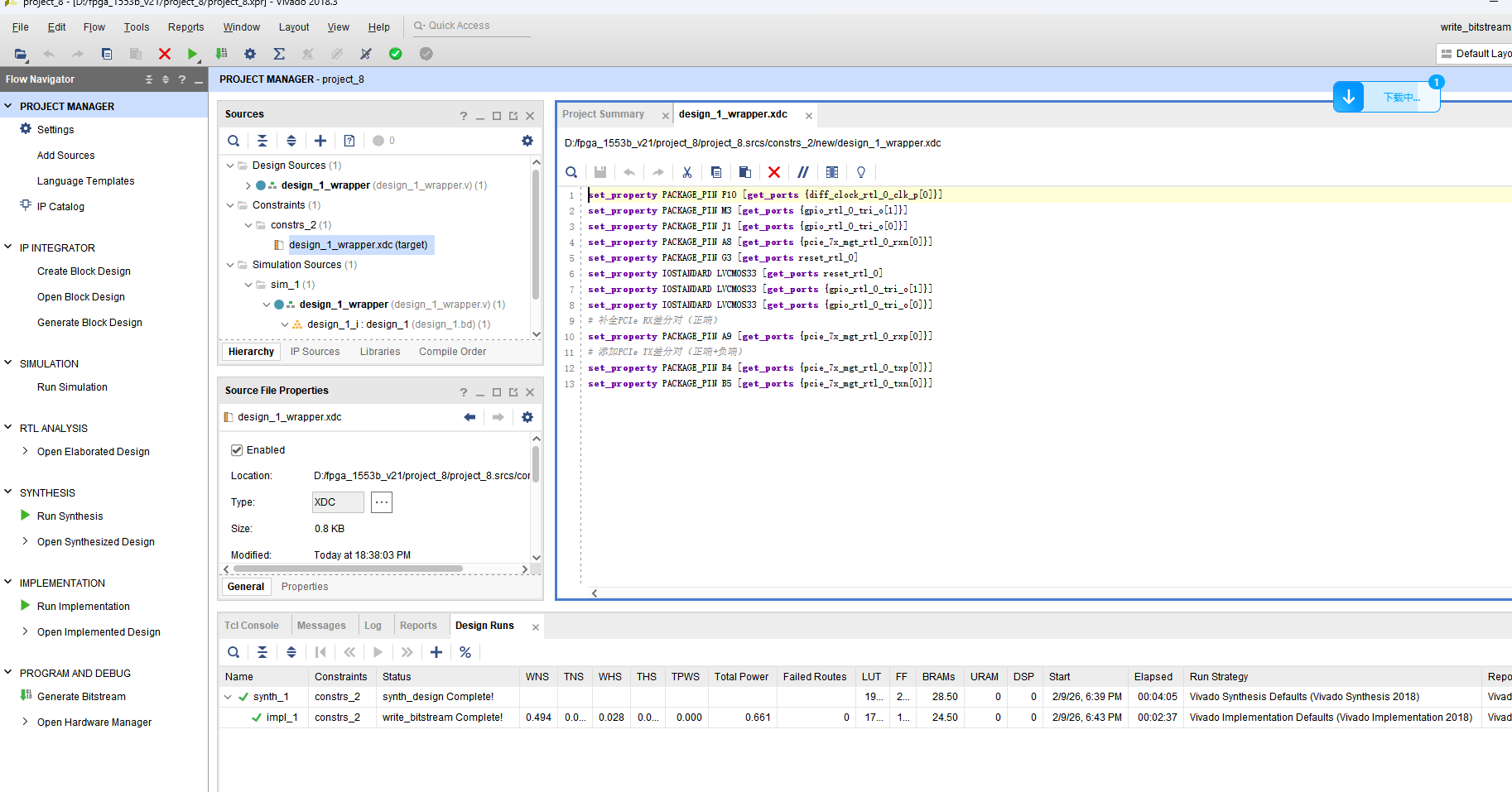

2. 位流未正确加载

- 原因:虽然你说位流可以正常下载,但可能加载顺序或时序有问题。

- 解决方法:

- 确认FPGA的启动流程是否正确,包括JTAG下载、配置文件加载等。

- 使用

hw_manager工具验证位流是否已正确加载。 - 添加调试信号(如LED或串口打印)来确认FPGA是否正常工作。

三、操作系统与驱动问题

1. 驱动未安装或不兼容

- 原因:即使FPGA能正常工作,如果没有正确的驱动程序,操作系统也无法识别PCIe设备。

- 解决方法:

- 安装对应的驱动程序(如Windows下的INF文件或Linux下的内核模块)。

- 使用

Device Manager(Windows)或lspci(Linux)查看设备是否被识别。 - 如果设备被识别为“未知设备”,说明驱动未正确安装。

2. 用户权限或系统限制

- 原因:某些系统(如Linux)需要root权限才能访问PCIe设备。

- 解决方法:

- 使用

sudo执行相关命令。 - 修改udev规则,使普通用户也能访问设备。

四、软件/应用层问题

1. 应用程序未正确调用PCIe设备

- 原因:即使设备被识别,应用程序也可能因API调用错误而无法读取或写入。

- 解决方法:

- 使用标准的PCIe库(如

libpci、pyusb、DMA等)进行测试。 - 编写简单的测试程序,验证是否能读取设备信息(如Vendor ID、Device ID)。

2. 中断未正确处理

- 原因:PCIe设备依赖中断进行通信,若中断未正确配置,可能导致设备无响应。

- 解决方法:

- 在FPGA代码中确保中断信号正确生成并发送。

- 在主机端代码中注册中断处理函数。

五、调试建议

1. 使用工具辅助诊断

- Windows:

- 使用

Device Manager 检查设备状态。 - 使用

HWiNFO64 或 GPU-Z 查看PCIe设备信息。

- Linux:

- 运行

lspci 查看设备是否被识别。 - 使用

dmesg 查看内核日志。 - 使用

ethtool 或 ip link 检查网络设备状态。

2. 增加调试输出

- 在FPGA中添加调试信号(如LED、串口输出),用于判断设备是否被正确初始化。

- 在主机端添加日志输出,确认是否接收到数据或中断。

六、推荐排查步骤(有序列表)

-

检查硬件连接:

- 确认PCIe卡已正确插入。

- 检查电源是否足够。

- 尝试更换插槽或设备。

-

验证位流加载:

- 使用

hw_manager或Vivado Hardware Manager确认位流加载成功。 - 检查FPGA是否正常工作(如LED亮起、串口输出)。

-

检查PCIe IP核配置:

- 确认IP核的地址映射、中断、数据宽度等参数正确。

- 对比官方示例工程进行调试。

-

安装并验证驱动:

- 安装对应驱动,重启后检查设备是否被识别。

- 使用

lspci或Device Manager查看设备状态。

-

编写简单测试程序:

- 使用标准库或工具测试PCIe设备是否可读写。

- 检查是否能获取设备信息(如Vendor ID、Device ID)。

-

查看系统日志:

- Windows:

Event Viewer 或 Device Manager。 - Linux:

dmesg 或 /var/log/syslog。

七、示例代码片段(FPGA部分)

// 示例:PCIe IP核中断信号生成

always @(posedge clk) begin

if (reset_n) begin

irq <= 1'b0;

end else begin

if (some_condition) begin

irq <= 1'b1; // 触发中断

end else begin

irq <= 1'b0;

end

end

end

注意:具体实现需根据所使用的FPGA开发板和IP核文档进行调整。

如果你能提供更具体的FPGA型号、开发环境(如Xilinx Vivado、Intel Quartus)、PCIe设备型号等信息,我可以进一步帮你定位问题。