上午好☀️☀️☀️️

本答案参考通义千问

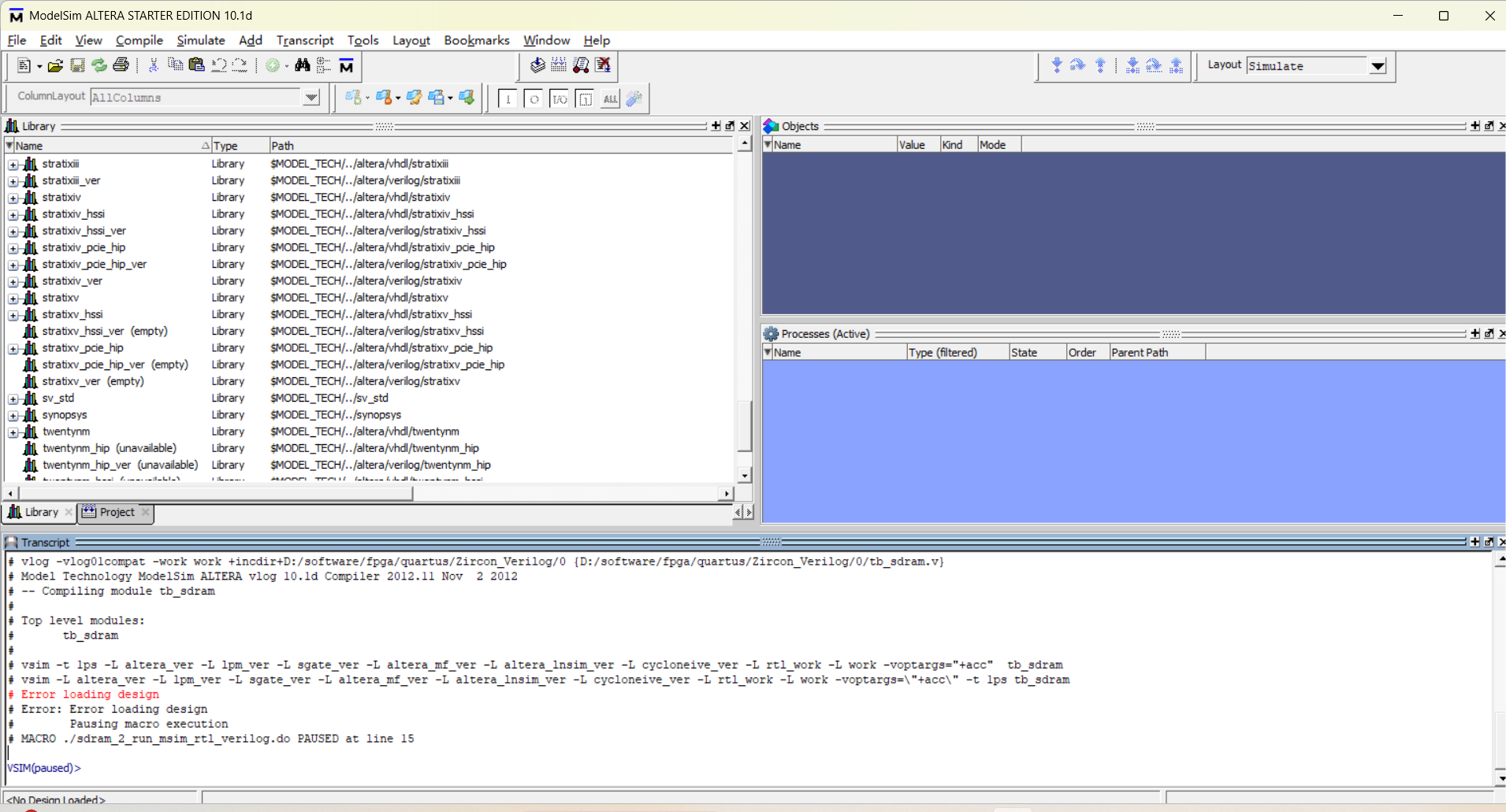

你遇到的 “Error loading design” 问题在 ModelSim(或其衍生版本如 QuestaSim、Intel® Quartus® Prime Simulator) 中是一个比较常见的错误,尤其是在使用 IP 核(如 Altera 的 altera_mf 库)时。根据你描述的情况,问题可能出在以下几方面:

🔍 一、问题分析

1. IP 核未正确编译

- 即使是新建工程,如果 IP 核没有被正确编译或加载,也会导致 “Error loading design”。

- 特别是在 Quartus 中生成 IP 核后,需要确保:

- 已完成 编译 IP 核(

Compile 或 Recompile); - 在 ModelSim 中加载了正确的库文件(如

altera_mf、lpm 等)。

2. ModelSim 与 Quartus 配置不一致

- 如果你之前用过某个工程,之后其他工程也出现此问题,可能是 环境配置 出现了问题。

- 检查是否:

- 正确设置了 环境变量(如

QUARTUS_ROOT); - 使用的是 正确的 ModelSim 路径;

- 在 ModelSim 中加载了 正确的库路径。

3. 库文件缺失或损坏

- 例如

altera_mf、lpm、cycloneiv 等库文件可能损坏或缺失。 - 这些库通常位于 Quartus 安装目录下的

ip 文件夹中。

✅ 二、解决方案(详细步骤)

第一步:检查 IP 核是否已正确编译

- 打开 Quartus II。

- 打开你的工程或新建一个工程。

- 右键点击 IP 核(如

alt_lfsr、alt_synchronizer 等),选择 "Recompile" 或 "Generate"。 - 确保 IP 核生成成功,无错误。

重点: 一定要在 Quartus 中编译完 IP 核后再进行仿真!

第二步:确认 ModelSim 与 Quartus 的配置一致

-

打开 ModelSim。

-

在命令行中输入以下命令,查看当前使用的 Quartus 路径:

setenv QUARTUS_ROOT

- 如果显示路径为空,说明环境变量未正确设置。

- 设置方法:

- Windows:右键“我的电脑” → “属性” → “高级系统设置” → “环境变量”;

- 添加

QUARTUS_ROOT 指向 Quartus 安装目录(如 C:\intelFPGA\20.1\quartus)。

-

在 ModelSim 中加载库文件:

- 打开 ModelSim,进入 File → Load Simulation Library;

- 加载

altera_mf、lpm、cycloneiv 等库(这些库通常在 Quartus 安装目录下的 ip 文件夹中)。

第三步:重新编译库文件(如 altera_mf)

- 打开 Quartus,进入 Tools → Options → EDA Tool Settings。

- 确保 ModelSim 仿真器被选中。

- 点击 "Recompile All Libraries",等待完成。

注意: 如果你在 ModelSim 中手动加载库,可能会覆盖 Quartus 自动生成的库,导致冲突。

第四步:尝试使用 QuestaSim 或 ModelSim 的新版本

- 有些旧版本的 ModelSim 可能对某些 IP 核支持不够好。

- 建议升级到 QuestaSim(Intel 提供的仿真工具)或 ModelSim SE 最新版本。

第五步:新建工程测试

- 新建一个简单工程,只包含一个简单的 Verilog 模块。

- 不使用任何 IP 核,直接进行仿真。

- 如果仍然报错,说明问题可能出在 ModelSim 安装或环境配置 上。

🧪 三、代码示例(可参考)

如果你的工程中使用了 IP 核,例如 alt_lfsr,请确保在仿真前正确实例化并连接:

module top(

input clk,

output reg [7:0] lfsr_out

);

// 实例化 LFSR IP 核

alt_lfsr #(

.width(8),

.seed(8'hAA)

) u_lfsr (

.clock(clk),

.q(lfsr_out)

);

endmodule

在 ModelSim 中,确保 altera_mf 库已正确加载。

🔁 四、常见错误排查思路总结

| 问题 | 解决方法 |

|------|----------|

| IP 核未编译 | 在 Quartus 中重新编译 IP 核 |

| 库文件缺失 | 重新编译所有库(Recompile All Libraries) |

| 环境变量错误 | 设置 QUARTUS_ROOT 环境变量 |

| ModelSim 版本过旧 | 升级到最新版(如 QuestaSim) |

| 工程配置错误 | 新建工程测试是否仍报错 |

✅ 五、最终建议

如果以上方法都试过仍无法解决,建议你:

- 重装 Quartus 和 ModelSim(注意:不要安装在中文路径下);

- 清理临时文件和缓存(如

.qdb、.lib、.tmp 等); - 联系 Intel 支持 或 访问 Intel 论坛 寻求帮助。

如果你能提供具体的错误信息(如完整报错内容),我可以进一步帮你定位问题。希望以上方法对你有帮助!