用vivado的dds ip产生了正弦波,想用过零比较的方法把正弦转换成方波。一开始把零点设为0,发现并不是,所以加了采集最大值最小值的代码,用中值作为零点,但仿真还是有些问题,想知道这些问题的原因

代码如下

reg [15:0] max;

reg [15:0] min;

wire [15:0] zero;

initial begin

max = 10000;

min = 10000;

end

always@(posedge sys_clk)

begin

if(sin_out_0 > max)

max <= sin_out_0;

end

always@(posedge sys_clk)

begin

if(sin_out_0 < min)

min <= sin_out_0;

end

assign zero = (max+min)/2;

always@(posedge sys_clk)

begin

if(sin_out_0 > zero)

squ_0 <= 1'b1;

else

squ_0 <= 1'b0;

end

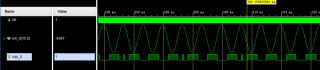

运行结果 波形为什么在一开始会有毛刺,300多ms后波形正常,且方波的0和1与预计的相反?

另外对仿真里正弦这类波形的值感到困惑,比如该仿真里可以通过调整数制和有符号看到正弦波的具体值且零点是0,但用在代码里却不对,波形每点的值是怎么确定的呢?