双边缘D触发器需要同时敏感上升沿和下降沿,我将clk取反赋给clk1,然后在always中同时对clk和clk1的信号上升沿敏感,这样不是就可以实现了吗?但是结果是错的,求指点下:

module top_module (

input clk,

input d,

output q

);

wire clk1;

assign clk1 = ~clk;

always@(posedge clk,posedge clk1) begin

q<=d;

end

endmodule

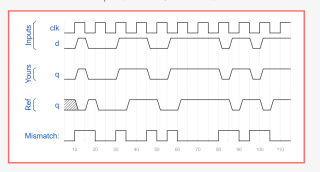

运行结果如下: