代码的目的:定义两个module块来模拟AB芯片,并且分别编号为0、1。FPGA是主模块,通过计数器产生0~5的控制信号,然后对控制信号进行分选后判断当前需要访问的是哪个芯片,然后再实例化该模块,同时得到其输出值。

FPGA代码:

module FPGA(clk,reset,cont,out); //主模块

input clk,reset; //时钟信号和复位信号

output [2:0] cont; //控制信号

output [7:0] out; //用于存放从芯片接收来的数据

reg [2:0] cont;

wire[7:0] out;

integer flag;

always @(posedge clk or negedge reset)//产生控制信号(计数器电路)

begin

if(!reset)

cont=0;

else if(cont==5) cont=0;

else cont=cont+1;

end

begin

A Amodule(.clk(clk),.cont(cont),.out(out));

B Bmodule(.clk(clk),.cont(cont),.out(out));

end

endmodule

A、B模块的定义:

module A (clk,cont,out);

input clk;

input [2:0]cont;

output [7:0] out;

reg[7:0] out;

always@(posedge clk)

begin

out=0;//初始化,防止出现不确定量

if(cont==0)

out=1; //若控制信号为0,则使能A芯片并输出数值1

end

endmodule

module B (clk,cont,out);

input clk;

input [2:0]cont;

output [7:0] out;

reg[7:0] out;

always@(posedge clk)

begin

out=0;//初始化

if(cont==1)

out=2; //若控制信号为1,则使能A芯片并输出数值2

end

endmodule

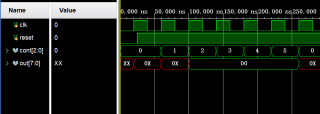

问题描述:在时序仿真过程中输出的结果如下图

如果将PFGA代码中的A、B模块的实例化删减剩A,则时域仿真结果正常

怀疑是出现了竞争与冒险现象,但是我不知道应该怎么改动!所以想请教一下各位这个代码应该怎么改。

(PS:我试过用在FPGA模块中的always模块外,用控制信号+case模块来实现分时实例化模块,但是报错说“控制信号”非常数,可能是因为没有在always模块内部使用case,但是如果在always模块中用case来实例化,就又会报错,因为模块的实例化没有办法在always模块里进行……所以很苦恼)