问题遇到的现象和发生背景

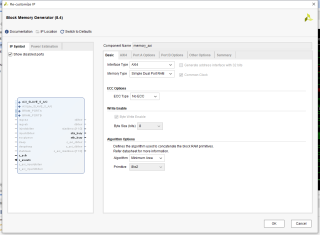

IP核生成:

testbench中想通过给IP核的端口进行赋值,来模拟单次读请求

问题相关代码,请勿粘贴截图

testbench

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2022/05/15 00:40:35

// Design Name:

// Module Name: ramtest

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module ramtest();

logic clk_i;

logic resetn_i;

//axi

logic rsta_busy;

logic rstb_busy;

logic [3:0] axi_awid;

logic [31:0] axi_awaddr;

logic [7:0] axi_awlen;

logic [2:0] axi_awsize;

logic [1:0] axi_awburst;

logic axi_awvalid;

logic axi_awready;

logic [31:0] axi_wdata;

logic [3:0] axi_wstrb;

logic axi_wlast;

logic axi_wvalid;

logic axi_wready;

logic [3:0] axi_bid;

logic [1:0] axi_bresp;

logic axi_bvalid;

logic axi_bready;

logic [3:0] axi_arid;

logic [31:0] axi_araddr;

logic [7:0] axi_arlen;

logic [2:0] axi_arsize;

logic [1:0] axi_arburst;

logic axi_arvalid;

logic axi_arready;

logic [3:0] axi_rid;

logic [31:0] axi_rdata;

logic [1:0] axi_rresp;

logic axi_rlast;

logic axi_rvalid;

logic axi_rready;

memory_axi memory(

.rsta_busy (rsta_busy ),

.rstb_busy (rstb_busy ),

.s_aclk (clk_i ), // input wire s_aclk

.s_aresetn (resetn_i ),

.s_axi_awid (axi_awid ),

.s_axi_awaddr (axi_awaddr ),

.s_axi_awlen (axi_awlen ),

.s_axi_awsize (axi_awsize ),

.s_axi_awburst (axi_awburst ),

.s_axi_awvalid (axi_awvalid ),

.s_axi_awready (axi_awready ),

.s_axi_wdata (axi_wdata ),

.s_axi_wstrb (axi_wstrb ),

.s_axi_wlast (axi_wlast ),

.s_axi_wvalid (axi_wvalid ),

.s_axi_wready (axi_wready ),

.s_axi_bid (axi_bid ),

.s_axi_bresp (axi_bresp ),

.s_axi_bvalid (axi_bvalid ),

.s_axi_bready (axi_bready ),

.s_axi_arid (axi_arid ),

.s_axi_araddr (axi_araddr ),

.s_axi_arlen (axi_arlen ),

.s_axi_arsize (axi_arsize ),

.s_axi_arburst (axi_arburst ),

.s_axi_arvalid (axi_arvalid ),

.s_axi_arready (axi_arready ),

.s_axi_rid (axi_rid ),

.s_axi_rdata (axi_rdata ),

.s_axi_rresp (axi_rresp ),

.s_axi_rlast (axi_rlast ),

.s_axi_rvalid (axi_rvalid ),

.s_axi_rready (axi_rready )

);

initial begin

clk_i <= 1;

forever begin

#10 clk_i <= ~clk_i;

end

end

initial begin

resetn_i <= 1;

#10 resetn_i <= 0;

end

initial begin

axi_arvalid <= 1'd0;

#50 axi_arvalid <= 1'd1;

end

initial begin

axi_arid <= '0;

axi_araddr <= '0;

axi_arlen <= '0;

axi_arsize <= '0;

axi_arburst <= '0;

#50

axi_arid <= 4'd1;

axi_araddr <= 32'd100;

axi_arlen <= 8'd0;

axi_arsize <= 3'd0;

axi_arburst <= 2'd0;

end

initial begin

axi_awid <= '0;

axi_awaddr <= '0;

axi_awlen <= '0;

axi_awsize <= '0;

axi_awburst <= '0;

axi_awvalid <= '0;

axi_wdata <= '0;

axi_wstrb <= '0;

axi_wlast <= '0;

axi_wvalid <= '0;

axi_rready <= '0;

end

endmodule

运行结果及报错内容

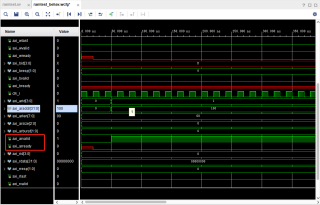

arvalid信号有效之后,arready始终没有拉高,数据也没有读取成功

我想要达到的结果

单次读请求读到数据