问题遇到的现象和发生背景

协议芯片接收arinc429总线数据,通过spi总线与fpga连接,如何实现上位机通过pcie对数据的读写

我的解答思路和尝试过的方法

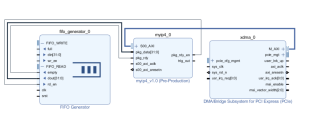

协议芯片接收Arinc429总线数据,通过spi接口传输到FPGA中,存储到fifo中,自定义axi4 IP 核,作为FIFO与xdma IP核的转换,fifo中的数据写入axi4 IP核中,上位机发送读数据命令读取数据。当fifo不为空时,输出empty为0,此时,读使能pkg_rdy_en置1;下个时钟周期,将fifo中一个数据写入axi4 ip核,读使能置0,trig_out置1,触发上位机发送读数据报文,读出数据,通过监视握手信号,读完数据后,读使能重新置1,当empty为1时,停止读。

大致连接关系如图,不是很严谨

我想要达到的结果

这个思路对吗,pcie核只能接收来自上位机的报文吗,它能自己发报文吗,怎么发,有没有能够长时间联系解惑