代码如下

module Clock_divide(clk,rst_n,clk_10M,clk_30M,locked);

input clk;

input rst_n;

output clk_10M;

output clk_30M;

output locked;

clk_wiz_0 instance_name

(

.clk_10M(clk_10M),

.clk_30M(clk_30M),

.locked(locked),

.reset(rst_n),

.clk_in1(clk));

endmodule

仿真文件

module tb_Clock_divide;

parameter PERIOD = 10;

reg clk = 0 ;

reg rst_n = 0 ;

wire clk_10M ;

wire clk_30M ;

wire locked ;

always #(PERIOD/2) clk=~clk;

initial

begin

#(PERIOD*10) rst_n = 1;

end

Clock_divide u_Clock_divide (

.clk ( clk ),

.rst_n ( rst_n ),

.clk_10M ( clk_10M ),

.clk_30M ( clk_30M ),

.locked ( locked )

);

endmodule

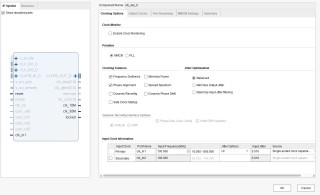

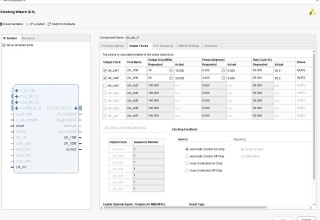

时钟IP设置