FPGA对ADC0809控制程序 ,用quaturs联合modelsim仿真时,总是NO DATA!

相关代码

源程序:

`timescale 1 ns / 1 ps

////////////////////////////////////////////////////////////////////////////////////

// Company: SMG

// Engineer: John Liu

//

// Create Date: 21:02:51 07/05/2022

// Design Name:

// Module Name: ADC0809

// Project Name: ADC0809

// Target Devices: EP3C25E144CBN & ADC0809

// Tool versions: 13.0

// Description: Interface Control for ADC0809

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////////

module ADC0809(

//input

input clk,

input rst_n,

input [2:0] add_in, //外部控制的通道选择信号

input [7:0] data_fromAD,

input EOC,

//output

output [2:0] add_out, //FPGA给ADC0809的通道选择信号

output [7:0] show_out, //传给上位机进行显示

output reg ALE, //d地址锁存允许信号

output reg START,

output reg OE, //输出允许信号

output reg clk_adc //ADC芯片的输入时钟

);

//参数

//状态机的8个状态常量

parameter IDLE1 = 3'b000,

ALE2 = 3'b001,

START_P3 = 3'b010,

START_N4 = 3'b011,

CHECK_EOC_P5 = 3'b100,

CHECK_EOC_N6 = 3'b101,

OE7 = 3'b110,

SEND_DATA8 = 3'd111;

parameter NUM = 50;

//定义中间变量

//reg [2:0] p_state ;

//reg [2:0] n_state ;

reg [2:0] state;

//reg ALE ;

//reg OE ;

//reg START;

reg [7:0] data_temp;

reg [7:0] count ; //分频器

//reg clk_adc; //adc时钟500kHZ

//时钟分频50MHz,20ns一个周期,现在要500KHz///////////////////////////////////

always@ (posedge clk or negedge rst_n) begin

if(!rst_n) begin

//p_state <= st0;

count <= 8'b0;

clk_adc <= 1'b0;

end

else if ((count==NUM-1)&& ( clk == 1'b1 )) begin

count <= 8'b0;

clk_adc <= ~clk_adc;

end

else

count = count +1'b1;

end

//三位地址信号传递//////////////////////////////////////////////////////////////

assign add_out = add_in;

//状态机////////////////////////////////////////////////////////////////////////

always@ (posedge clk_adc or negedge rst_n) begin

if(!rst_n) begin

state <= IDLE1; //进入初始状态

ALE <= 1'b0; //输出给ADC的地址锁存允许信号 初始化一下

START <= 1'b0; //输出给ADC的转化启动信号 初始化一下

OE <= 1'b0; //输出给ADC的数据输出允许信号 初始化一下

data_temp <= 8'd0;

end

else begin

case(state)

IDLE1: begin //1

ALE <= 1'b0;

START <= 1'b0;

OE <= 1'b0;

state <= ALE2;

end

ALE2: begin //2

ALE <= 1'b1;

START <= 1'b0;

OE <= 1'b0;

state <= START_P3;

end

START_P3: begin //3

ALE <= 1'b0;

START <= 1'b1;

OE <= 1'b0;

state <= START_N4;

end

START_N4: begin //4

ALE <= 1'b0;

START <= 1'b0;

OE <= 1'b0;

state <= CHECK_EOC_P5;

end

CHECK_EOC_P5: begin //5

if(EOC == 1'b1)

state = CHECK_EOC_P5;

else

state = CHECK_EOC_N6; //检测到了低电平,说明开始转换

end

CHECK_EOC_N6: begin //6

if(EOC == 1'b0)

state <= CHECK_EOC_N6;//等待转换的结束

else

state <= OE7;

end

OE7: begin //7

OE <= 1'b1;

state <= SEND_DATA8;

end

SEND_DATA8: begin //8

data_temp <= data_fromAD;

state <= IDLE1;

end

default: begin

ALE <= 1'b0;

START <= 1'b0;

OE <= 1'b0;

state <= IDLE1;

end

endcase

end

end

//assign add_out = 3'b000;//选通IN0

assign show_out = data_temp;

endmodule

tb程序:

`timescale 1 ns/ 1 ps

module ADC0809_vlg_tst();

// constants

// general purpose registers

reg eachvec;

// test vector input registers

reg EOC;

reg [2:0] add_in;

reg clk;

reg [7:0] data_fromAD;

reg rst_n;

// wires

wire ALE;

wire OE;

wire START;

wire [2:0] add_out;

wire clk_adc;

wire [7:0] show_out;

parameter T = 20; //时钟周期为20ns

// assign statements (if any)

ADC0809 i1 (

// port map - connection between master ports and signals/registers

.ALE(ALE),

.EOC(EOC),

.OE(OE),

.START(START),

.add_in(add_in),

.add_out(add_out),

.clk(clk),

.clk_adc(clk_adc),

.data_fromAD(data_fromAD),

.rst_n(rst_n),

.show_out(show_out)

);

initial

begin

// code that executes only once

// insert code here --> begin

clk = 0;

rst_n <= 0;

#(T+1)

rst_n <=1;

data_fromAD <= 8'h0; //暂且模拟输入初始化

EOC = 1'b1; //转换结束状态初始化

end

always #(T/2) clk = ~clk;

always add_in = 3'b010;

always @(negedge START) begin

#3000 //t_EOC

EOC <= 1'b0;

data_fromAD <= data_fromAD + 1'b1; //

#99000 //t_C

EOC <= 1'b1;

end

endmodule

运行结果及报错内容

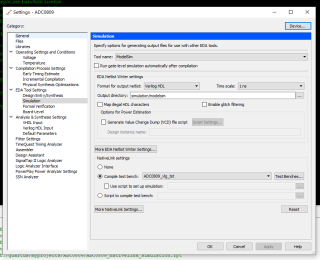

设置:

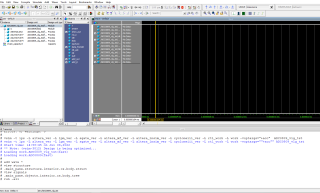

结果: