问题遇到的现象和发生背景

做呼吸灯的设计,开发板20ns一个系统时钟周期。将2s分为1000个2ms作为呼吸灯变化周期,将2ms分为1000个2us作为呼吸灯变化单元。分别用cnt_2us、cnt_2ms、cnt_2s作为记时2us,2ms,2s的计数器。

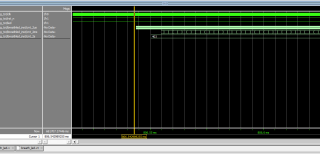

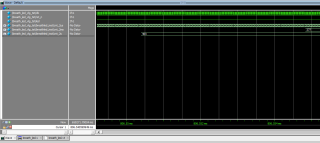

用quartus调用modelsim仿真后,将计数器的结果也显示出来,可是这三个计数器一开始却是没有值的!

问题相关代码

//50Mhz,,计数1次20ns

module breath_led(

input wire clk,

input wire rst_n,

output reg led

);

/*

parameter CNT_2s_END = 999? //??2s????

parameter CNT_2ms_END = 999? //??2ms????

parameter CNT_2us_END = 99? //??2us????

*/

reg [9:0] cnt_2s; //999转换为二进制需要10个位宽

reg [9:0] cnt_2ms;

reg [6:0] cnt_2us;

//--------------------< 2us计数>------------------------------------------

always@(posedge clk or negedge rst_n)

if (rst_n==0)

cnt_2us <= 0;

else if(cnt_2us == 99)

cnt_2us <= 0;

else

cnt_2us <= cnt_2us+1;

//--------------------< 2ms计数 >------------------------------------------

always@ (posedge clk or negedge rst_n)

if (rst_n ==0)

cnt_2ms <= 0;

else if( (cnt_2ms == 999) && (cnt_2us == 99) )

cnt_2ms <= 0;

else if( (cnt_2us==99) && (cnt_2ms <999) )

cnt_2ms <= cnt_2ms+1;

//--------------------< 2s计数 >------------------------------------------

always@ (posedge clk or negedge rst_n)

if (rst_n ==0)

cnt_2s <= 0;

else if( (cnt_2ms == 999) && (cnt_2us == 99) && (cnt_2s == 999) )

cnt_2s <= 0;

else if( (cnt_2us==99) && (cnt_2ms==999) )

cnt_2s <= cnt_2s+1;

//--------------------< LED >------------------------------------------

always@ (posedge clk or negedge rst_n)

if(rst_n == 0)

led <= 0;

else if(cnt_2s > cnt_2ms)

led <= 1;

else

led <=0;

endmodule

tb代码:

`timescale 1 ns/ 1 ps

module breath_led_vlg_tst();

parameter period = 20;

//localparam period = 20;

//--------------------< 端口>------------------------------------------

reg clk;

reg rst_n;

wire led;

//--------------------< 模块例化>------------------------------------------

breath_led breathled_inst(

.clk(clk),

.rst_n(rst_n),

.led(led)

);

//--------------------< 初始信号>------------------------------------------

initial begin

clk=0; //clk阻塞性赋值

rst_n<=0;

#100 //延时100ns便于观察波形

rst_n<=1;

end

//--------------------< 设计输入信号 >-----------------------------------------

always #(period/2) clk=~clk;

endmodule

运行结果及报错内容