hdlbits中的一个题目

module top_module (

input clk,

input d,

output q

);

wire clk1,sw;

always@(posedge clk)begin

clk1<=clk;

end

always@(posedge clk)begin

sw<=clk1&(~clk);

sw<=clk1&(~clk); //找到下降沿

end

always@(posedge clk or posedge sw)begin//下降沿的上升沿就是clk的下降沿,但是会差一个周期

q<=d;

end

endmodule

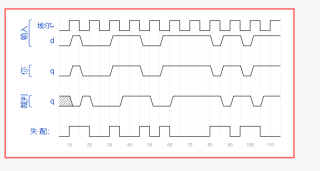

运行结果

错误

Critical Warning (10237): Verilog HDL warning at top_module.v(18): can't infer register for assignment in edge-triggered always construct because the clock isn't obvious. Generated combinational logic instead File: /home/h/work/hdlbits.8931483/top_module.v Line: 18

这是一种隐晦的说法:你把你的触发器编码错了。Verilog需要以逻辑频率合成器可以理解的风格进行编码,特别是在复位和使能信号时。常见原因包括在敏感度列表中指定异步重置(看起来像两个时钟),但在 if-then-else 结构中不以这种方式运行,或者尝试将看起来根本不像重置和启用的典型编码样式的代码组合在一起。

Warning (15610): No output dependent on input pin "clk" File: /home/h/work/hdlbits.8931483/top_module.v Line: 2

此警告表示这些输入引脚未被任何东西使用(或不影响电路的行为)。如果这种情况发生在您知道不应该忽略的输入上,则可能表示存在错误。

先找到一个下降沿的波形,然后用它的上升沿作为原来时钟下降沿,再用always去赋值,但是不能出现预期结果。