有四百多个寄存器,如何设计总线读取功能?

目前我们公司的传统做法是使用MUX,但之前没有那么多寄存器,现在有个新的设计,需要实现四百多个寄存器。

所有的寄存器已经按功能分别打包到各个功能模块了,如果按公司传统做法,需要把寄存器的值输出,四百多个,我感觉太麻烦了。不知道有没有更好的办法呢。

总线的的协议解析模块是固化好的,我要实现的是把寄存器的值给这个解析模块,而不是直接给到总线接口,所以也不能用三态门来做。

有四百多个寄存器,如何设计总线读取功能?

目前我们公司的传统做法是使用MUX,但之前没有那么多寄存器,现在有个新的设计,需要实现四百多个寄存器。

所有的寄存器已经按功能分别打包到各个功能模块了,如果按公司传统做法,需要把寄存器的值输出,四百多个,我感觉太麻烦了。不知道有没有更好的办法呢。

总线的的协议解析模块是固化好的,我要实现的是把寄存器的值给这个解析模块,而不是直接给到总线接口,所以也不能用三态门来做。

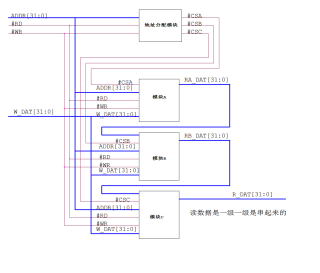

FPGA 需要自己定义一个类似的二级总线。(一级是与CPU互联的总线)

需要编写个模块将一级总线转成二级总线。

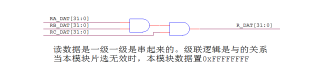

图中是自己定义的FPGA内部模块读写的二级总线

模块左边是输入,右边是输出