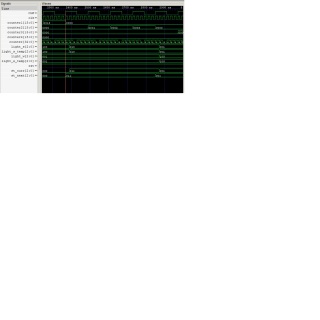

**结果__**:light_s与light_w都是输出,但是这个三段式中,st_curr也即现态始终不能立即变为st_next,尝试过改阻塞非阻塞但没有任何用输出结果都一样。

**题目:__**一个红绿灯,s,w,小clk生成大CLk,经过一定的周期变换红绿灯

问题遇到的现象和发生背景

问题相关代码,请勿粘贴截图

/*红绿灯 两个灯,

对其中一个进行状态分析,经过一定的大CLK后转变状态*/

/*

未完善每个灯时间

current状态始终会差一个周期变为next状态(阻塞or非阻塞)

☹☹☹☹☹☹☹☹

*/

module maincode(

input clk,

input rst,

output [2:0]light_s,

output [2:0]light_w

);

parameter Green=0;

parameter Red=1;

parameter Red1=2;

parameter Yellow=3;

reg [2:0]light_s_temp;

reg [2:0]light_w_temp;

assign light_s=light_s_temp;

assign light_w=light_w_temp;

reg [2:0]st_curr=Green;

reg [2:0]st_next=Green;

reg CLK;

reg [32:0]counter;

always @(posedge clk) //1M=10^6

begin

if(counter<=2)

begin

CLK<=0;

counter+=1;

end

else if(counter<=4)

begin

CLK<=1;

counter+=1;

end

else

counter=0;

end

//第一段 时序逻辑

always @(posedge clk)//同步清零

begin

if(!rst)

st_curr=Green;

else

st_curr=st_next;

end

reg [15:0]counter1=0;

reg [15:0]counter2=0;

reg [15:0]counter3=0;

reg [15:0]counter4=0;

//第二段 组合逻辑

always @(posedge CLK)

begin

case(st_curr)

Green:

begin

if(counter1<19)

begin

counter1=counter1+1;

st_next<=Green;

end

else if(counter1==19)

begin

counter1=0;

st_next<=Yellow;

end

end

Yellow:

begin

if(counter2<3)

begin

counter2=counter2+1;

st_next<=Yellow;

end

else if(counter2==3)

begin

counter2=0;

st_next<=Red;

end

end

Red:

begin

if(counter3<57)

begin

counter3+=1;

st_next<=Red;

end

else if(counter3==57)

begin

counter3=0;

st_next<=Red1;

end

end

Red1:

begin

if(counter4<3)

begin

counter4+=1;

st_next<=Red1;

end

else if(counter4==3)

begin

counter4=0;

st_next<=Green;

end

end

endcase

end

//第三段 时序逻辑

//[2:0]========0 1代表G Y R的亮与灭

always @(posedge clk)

begin

if(st_curr==Green)

begin

light_s_temp<=3'b100;

light_w_temp<=3'b001;

end

else if(st_curr==Yellow)

begin

light_s_temp<=3'b010;

light_w_temp<=3'b001;

end

else if(st_curr==Red)

begin

light_s_temp<=3'b001;

light_w_temp<=3'b100;

end

else

begin

light_s_temp<=3'b001;

light_w_temp<=3'b010;

end

end

endmodule