module traffic(en,clk,rst,num1,num2,light1,light2,out1,out2,out3,out4,in1,in2);

input en,clk,rst,in1,in2; //en为使能端,in1,in2控制红灯和绿灯亮的时间

output reg[7:0]num1,num2;

output reg[2:0]light1,light2;

output reg[6:0]out1,out2,out3,out4;//输出部分四个数码管

reg tim1,tim2;

reg [1:0]state1,state2;

reg [7:0]red1,red2,green1,green2,yellow1,yellow2;

parameter s0=2'b00,s1=2'b01,s2=2'b10,s3=2'b11;//三个循环状态

reg[31:0]count;

reg clk1hz;

always@(en or in1 or in2)

if(en)

begin//设置计数初值

if(in1)begin green1<=8'b00110000;red2<=8'b00110000;end

else begin green1<=8'b01100000;red2<=8'b01100000;end

if(in2)begin green2<=8'b00100000;red1<=8'b00100000;end

else begin green2<=8'b01000000;red1<=8'b01000000;end

yellow1<=8'b00000101;yellow2<=8'b00000101;

end

else begin

green1<=8'b0;green2<=8'b0;

red1<=8'b0;red2<=8'b0;

yellow1<=8'b0;yellow2<=8'b0;

end

always@(posedge clk)//分频器,50MHz

if(count==32'd25000000)begin clk1hz<=1;count<=count+1;end

else if(count==32'd50000000)begin clk1hz<=0;count<=0;end

else count<=count+1'b1;

always@(posedge clk1hz)//主干道

begin

if(rst)//复位控制

begin

state1<=s0;

light1<=3'b001;

num1<=green1;

end

else if(en)//使能端有效开始控制计数

begin

if(!tim1)//计数控制

begin//交通灯点亮

tim1<=1;

case(state1)

s0:begin num1<=green1;light1<=3'b001;state1<=s1;end

s1:begin num1<=yellow1;light1<=3'b010;state1<=s2;end

s2:begin num1<=red1;light1<=3'b100;state1<=s0;end

default:light1<=3'b100;

endcase

end

else

begin//倒数计时

if(num1>0)

if(num1[3:0]==0)

begin

num1[3:0]<=4'b1001;

num1[7:4]<=num1[7:4]-1'b1;//十位数减一

end

else

num1[3:0]<=num1[3:0]-1'b1;//个位数减一

if(num1==1)tim1<=0;

end

end

else

begin//使能端无效时全部变为初态

light1<=3'b111;

state1<=s0;

tim1<=0;

end

end

always@(posedge clk1hz)

begin

if(rst)

begin

light2<=3'b100;

num2<=red2;

end

else if(en)

begin

if(!tim2)

begin

tim2<=1;

case(state2)

s0:begin num2<=red2;light2<=3'b100;state2<=s1;end

s1:begin num2<=yellow2;light2<=3'b010;state2<=s2;end

s2:begin num2<=green2;light2<=3'b001;state2<=s3;end

s3:begin num2<=yellow2;light2<=3'b010;state2<=s0;end

default:light2<=3'b100;

endcase

end

else

begin

if(num2>0)

if(num2[3:0]==0)

begin

num2[3:0]<=4'b1001;

num2[7:4]<=num2[7:4]-1'b1;

end

else num2[3:0]<=num2[3:0]-1'b1;

if(num2==1) tim2<=0;

end

end

end

always@(posedge clk)

begin//七段数码管显示

case(num1[3:0])

4'b0000:out1<=~7'b0111111;

4'b0001:out1<=~7'b0000110;

4'b0010:out1<=~7'b1011011;

4'b0011:out1<=~7'b1001111;

4'b0100:out1<=~7'b1100110;

4'b0101:out1<=~7'b1101101;

4'b0110:out1<=~7'b1111101;

4'b0111:out1<=~7'b0000111;

4'b1000:out1<=~7'b1111111;

4'b1001:out1<=~7'b1101111;

default:out1<=7'b0111111;

endcase

end

always@(posedge clk)

begin

case(num1[7:4])

4'b0000:out2<=~7'b0111111;

4'b0001:out2<=~7'b0000110;

4'b0010:out2<=~7'b1011011;

4'b0011:out2<=~7'b1001111;

4'b0100:out2<=~7'b1100110;

4'b0101:out2<=~7'b1101101;

4'b0110:out2<=~7'b1111101;

4'b0111:out2<=~7'b0000111;

4'b1000:out2<=~7'b1111111;

4'b1001:out2<=~7'b1101111;

default:out2<=7'b0111111;

endcase

end

always@(posedge clk)

begin

case(num2[3:0])

4'b0000:out3<=~7'b0111111;

4'b0001:out3<=~7'b0000110;

4'b0010:out3<=~7'b1011011;

4'b0011:out3<=~7'b1001111;

4'b0100:out3<=~7'b1100110;

4'b0101:out3<=~7'b1101101;

4'b0110:out3<=~7'b1111101;

4'b0111:out3<=~7'b0000111;

4'b1000:out3<=~7'b1111111;

4'b1001:out3<=~7'b1101111;

default:out3<=7'b0111111;

endcase

end

always@(posedge clk)

begin

case(num2[7:4])

4'b0000:out4<=~7'b0111111;

4'b0001:out4<=~7'b0000110;

4'b0010:out4<=~7'b1011011;

4'b0011:out4<=~7'b1001111;

4'b0100:out4<=~7'b1100110;

4'b0101:out4<=~7'b1101101;

4'b0110:out4<=~7'b1111101;

4'b0111:out4<=~7'b0000111;

4'b1000:out4<=~7'b1111111;

4'b1001:out4<=~7'b1101111;

default:out4<=7'b0111111;

endcase

end

endmodule

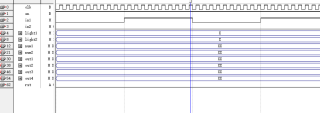

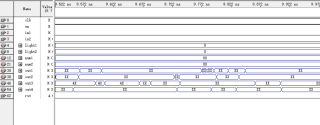

在仿真波形时输出很奇怪,有没有人知道仿真应该怎么设置呀。软件是quartus2