最近在做一个设计,遇到一段代码,

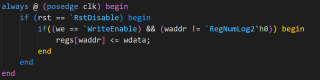

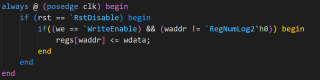

第一段代码表示对寄存器进行写操作

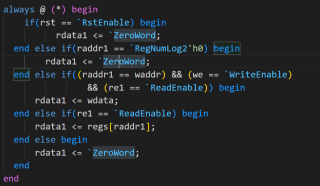

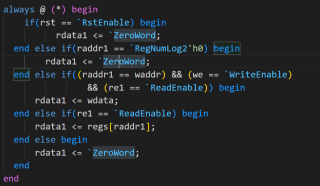

第二段代码表示对寄存器进行读操作

代码其实不重要,主要就是不太明白verilog设计cpu时什么情况下才需要输入时钟信号?也就是下面两行代码使用的情况

always @ (*) begin

always @ (posedge clk) begin

最近在做一个设计,遇到一段代码,

很多人都有这种困惑

很多人不知道什么时候该用组合逻辑,什么时候该用带时钟的时序逻辑。

用单纯的组合逻辑 always @ (*) 写代码,由于代码中不考虑延时,编程逻辑复合绝大多数软件工程师的编程思路。

但是 FPGA Verilog 是硬件描述语言,单纯的组合逻辑中存在的延时,冒险竞争,同步等问题是无法解决的。只建议在低速率逻辑中大范围使用组合逻辑。

在一些高速率应用中还是需要用带时钟的时序逻辑 always @ (posedge clk) 来设计代码。

时序逻辑由于寄存器赋值需要在下个时钟的边沿才能体现,在设计代码中确实比较难以理解。

这也是很多初学者觉的难学、畏惧的地方。

学习并掌握状态机的时序设计。

在代码设计中需要有电路设计的某些思想和思路。

在高速时序设计中需要采用流水线时序逻辑设计