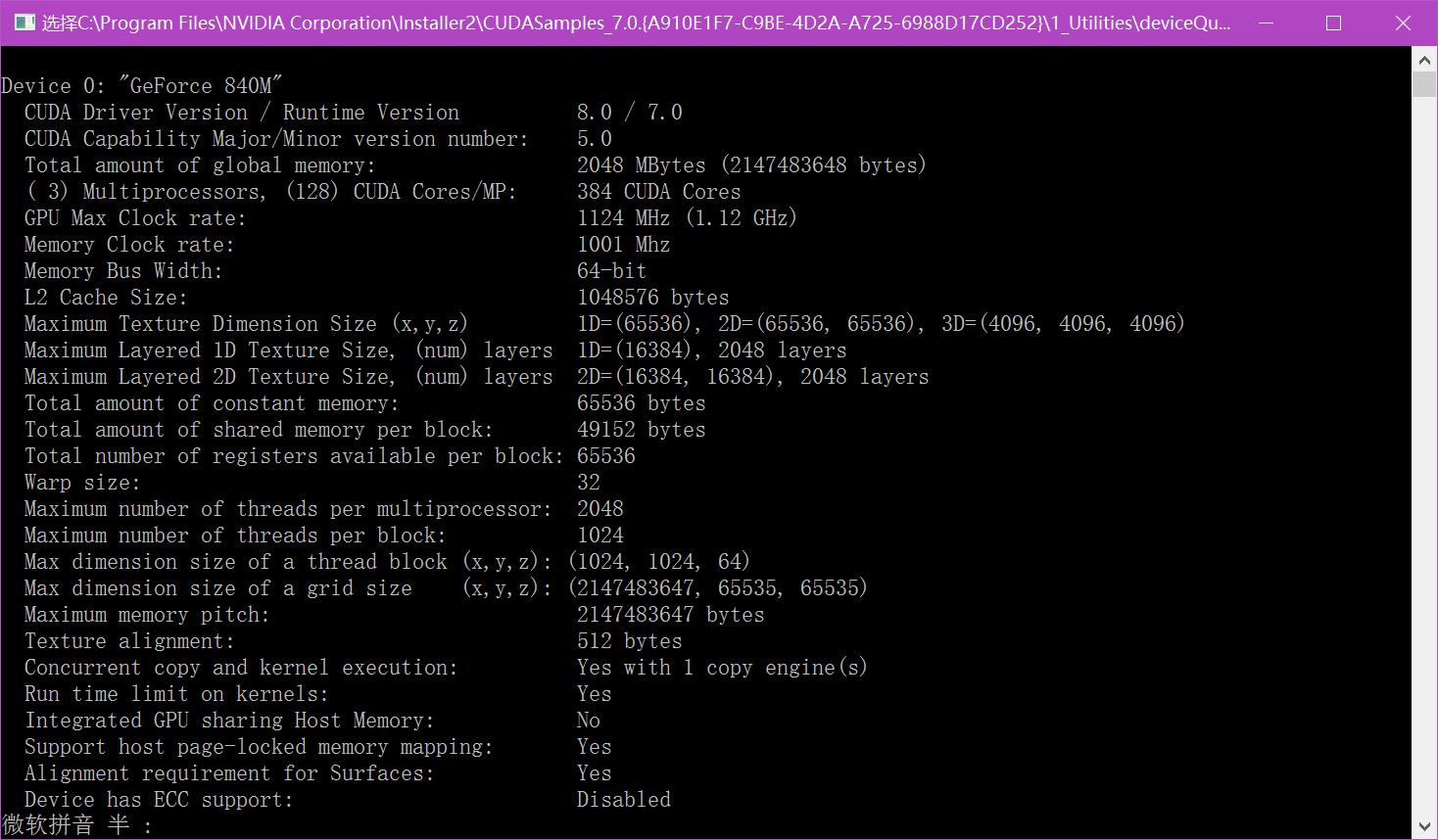

我对一幅图像做处理,640X480,对每个像素我分配了一个thread,即我每个block分配了640个thread,分配了480

个block。然后我对另一幅2048X1536的图像操作,我每个block分配了1024个thread,共分配了1536X2个block。用

同样的算法,问题规模增加了10倍,我不理解的是为什么运行时间也增加了10倍。不是只会增加一点读取数据的时间吗。

对CUDA的运行原理不是很了解,忘大神指教。

CUDA加速为什么没有并行的效果

- 写回答

- 好问题 0 提建议

- 追加酬金

- 关注问题

- 邀请回答

-

4条回答 默认 最新

MingChaoSun 2016-04-06 13:52关注

MingChaoSun 2016-04-06 13:52关注CUDA编程的优化可不只是一味增加线程,线程增加到一定程度就不能加速了,反而会越来越慢,因为实际上GPU的处理单元还是有限的,增大线程只能在一定程度上隐藏global memory的latency,题主最好去系统学一下CUDA,不然写出来的程序是比较差的,常规的优化方法还有非常多,要想优化好一个CUDA程序,首先要设计比较合理的并行算法,举个例子来说树状加法并行就会比正常相加快很多,第一步是首先尽量优化内存带宽,因为内存带宽一般是程序的瓶颈,GPU相比CPU的一大优势就在于有非常大的内存带宽,有的能到150GB/s,这里面不单单是线程,比如考虑访问global内存的顺序,如果是顺序访问内存,而不是跳跃访问,大概会有3-8倍的加速,在线程方面使用基本没有latency的share memory 也是一个加速的手段,优化好内存带宽之后还有很多的优化技术,比如优化指令流,在误差可接受的情况下,使用CUDA算术指令集中的快速指令,避免多余的同步,资源均衡,与主机通信优化,尽量减少CPU与GPU间的传输,使用流和异步处理隐藏与主机的通信时间;使用zero-memory技术和Write-Combined memory提高可用带宽等等,所以建议去系统学一下,还是很有学问的~

解决 无用评论 打赏 举报

悬赏问题

- ¥15 关于#matlab#的问题:在模糊控制器中选出线路信息,在simulink中根据线路信息生成速度时间目标曲线(初速度为20m/s,15秒后减为0的速度时间图像)我想问线路信息是什么

- ¥15 banner广告展示设置多少时间不怎么会消耗用户价值

- ¥16 mybatis的代理对象无法通过@Autowired装填

- ¥15 可见光定位matlab仿真

- ¥15 arduino 四自由度机械臂

- ¥15 wordpress 产品图片 GIF 没法显示

- ¥15 求三国群英传pl国战时间的修改方法

- ¥15 matlab代码代写,需写出详细代码,代价私

- ¥15 ROS系统搭建请教(跨境电商用途)

- ¥15 AIC3204的示例代码有吗,想用AIC3204测量血氧,找不到相关的代码。