问题遇到的现象和发生背景

本人使用quartusII编写111序列检测的模块,用modelsim进行仿真,得到了想要的激励,但是输出结果不对,输入存在连续的111的时候,输出还是为0,且一直为0,到底是哪里错了?

问题相关代码

模块代码:

//序列检测器,检测111,采用Mealy型FSM

module seq_tec1(in, clk, rst, out);

input in, clk, rst;

output out;

reg out;//输出必须有指定类型

parameter [3:0] S0=4'b0001, S1=4'b0010,

S2=4'b0100, S3=4'b1000; //状态编码,采用独热one hot码。

//状态寄存器

reg [3:0] S; //S当前状态

reg [3:0] Snext; //Snext下一时刻状态

//状态转移方程,根据状态转移表可写出状态转移关系

always @(in or S)

begin

case(S)

S0: Snext = (in==1'b1)? S1 : S0;

S1: Snext = (in==1'b1)? S2 : S0;

S2: Snext = (in==1'b1)? S3 : S0;

S3: Snext = (in==1'b1)? S3 : S0;

default: Snext = S0;

endcase

end

//rst功能和clk功能

always @(negedge rst or posedge clk)

begin

if(~rst)

S <= S0;

else

S <= Snext;

end

//输出方程

always @(negedge rst or posedge clk)

begin

if(~rst) //按下复位键

out <= 1'b0;

else

case(S)

S0 , S1: out <= 1'b0;

S2 , S3: out <= (in == 1'b1) ? 1'b1 : 1'b0;

default: out <= 1'b0;

endcase

end

endmodule

tb代码:

`timescale 1 ps/ 1 ps

module seq_tec1_vlg_tst();

reg clk, rst;

wire in, out;

reg [23 : 0] data; //定义一个24位的寄存器用于存放待测数据码

parameter PERIOD = 20;

//==========模块例化====================//

seq_tec1 i1 (

.clk(clk),

.in(in),

.out(out),

.rst(rst)

);

//==========产生初始信号=================//

initial

begin

clk = 0; rst = 0;

#5 rst = 1;

#20 rst = 0;

data = 24'b0011_1111_1111_0000_1001_0100;

//#(PERIOD * 100) $stop; //执行100个时钟周期

$display("Running testbench");

end

//==========产生时钟信号================//

always #(PERIOD/2) clk = ~clk;

//========循环移位产生输入数据============//

always @(posedge clk)

#5 data = {data[22 : 0], data[23]}; //循环左移

assign in = data[23]; //将最高位输入到序列检测器中

endmodule

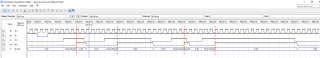

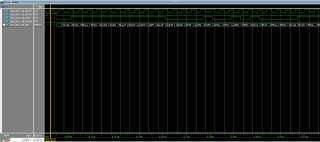

运行结果及

我想要达到的结果

通过quartusII自带的VWF仿真得到的: