刚开始接触RAM的设计,对输入输出数据、地址及位宽的概念与关系的理解有点混乱

part 1

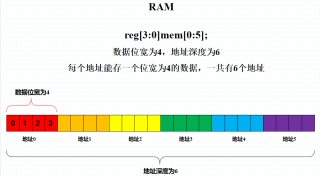

从书中看到Verilog定义一个存储器的语法格式为 reg [ 47 : 0 ] mem [ 0 : 255 ];

问题1:[ 47 : 0 ] 是不是可以理解为每一个地址可以存储一个位宽为48bits的数据?

问题2:[ 0:255 ] 是不是可以理解为一共有256个地址可以用来存储数据?

问题3:请问图片里的描述正确吗?

问题4:地址本身也要用一组二进制数来表示,那表示地址本身的二进制数的位宽该如何表示呢?

问题5:地址位宽和数据位宽之间有关联吗?如果二者有关联的话,在设计电路的时候应该注意些什么?