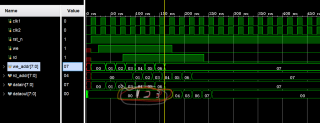

在编写双口ram中,一填加 if(!rst_n)

begin

for(i=0;i<7;i=i+1)

mem[i] <= 'b0;

end 这几句结果dataout中的123就没了。删去这几句结果就正确。请问是为什么?

module ram_8192

(

input wire clk1,//写时钟

input wire clk2,//读时钟

input wire rst_n,

input wire we,//写使能

input wire rd,//读使能

input wire [2:0] we_addr,//写地址

input wire [2:0] rd_addr,//读地址

input wire [7:0] datain,//写数据

output reg [7:0] dataout//读数据

);

reg [7:0]mem[7:0];

integer i;

always @(posedge clk1) begin

module ram_8192

(

input wire clk1,//写时钟

input wire clk2,//读时钟

input wire rst_n,

input wire we,//写使能

input wire rd,//读使能

input wire [2:0] we_addr,//写地址

input wire [2:0] rd_addr,//读地址

input wire [7:0] datain,//写数据

output reg [7:0] dataout//读数据

);

reg [7:0]mem[7:0];

integer i;

always @(posedge clk1) begin

if(!rst_n)

begin

for(i=0;i<7;i=i+1)

mem[i] <= 'b0;

end

else if (we == 1'b1) begin

mem[we_addr] <= datain;

end

end

always @(posedge clk2) begin

if (rd == 1'b1) begin

dataout <= mem[rd_addr];

end

else

dataout <='b0;

end

endmodule

else if (we == 1'b1) begin

mem[we_addr] <= datain;

end

end

always @(posedge clk2) begin

if (rd == 1'b1) begin

dataout <= mem[rd_addr];

end

else

dataout <='b0;

end

endmodule

tb文件

`timescale 1ns / 1ps

module ram_sim();

reg clk1,clk2;

reg rst_n;

reg we,rd;

reg [7:0] we_addr,rd_addr;

reg [7:0] datain;

wire[7:0] dataout;

initial begin

clk1 = 0;

clk2 = 0;

rst_n =0;

#10 rst_n = 1;

we = 0;

rd = 0;

we_addr = 0;

rd_addr = 0;

datain = 0;

end

always #10 clk1 = ~clk1;

always #10 clk2 = ~clk2;

initial begin

#25

we = 1;

#50

rd = 1;

#100

we = 0;

end

initial begin

#20

repeat(7)

#20

begin

we_addr = we_addr +1;

datain = datain + 1;

end

end

initial begin

#75

repeat(7)

#20

begin

rd_addr = rd_addr +1;

end

end

initial

#240

rd = 0;

ram_8192 inst_single_dualram(

.clk1 (clk1),

.clk2 (clk2),

.rst_n (rst_n),

.we (we),

.rd (rd),

.we_addr (we_addr),

.rd_addr (rd_addr),

.datain (datain),

.dataout (dataout)

);

endmodule

仿真图