FPGA的120+个普通IO,逻辑为0时(电压为0V),希望输出电平为1.2V,逻辑为1时(电压为1.2V),希望输出电平为2.4V,要怎么设计

FPGA的120+普通IO,逻辑为0时(电压为0V),希望输出电平为1.2V,逻辑为1时(电压为1.2V),希望输出电平为2.4V,要怎么设计

- 写回答

- 好问题 0 提建议

- 追加酬金

- 关注问题

- 邀请回答

-

1条回答 默认 最新

老皮芽子 2022-09-15 15:37关注

老皮芽子 2022-09-15 15:37关注以 XILINX FPGA举例

FPGA 管脚若干个 BANK 组成

每个BANK内的管脚的电压必须是一样的。

不同BANK的管脚的电压可以不一样。

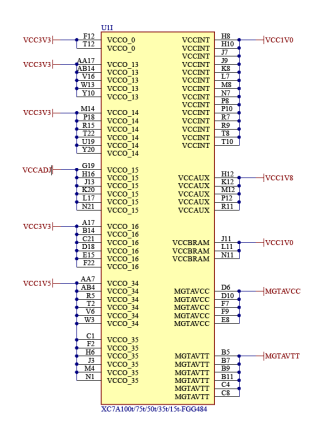

比如 XC7A100T 芯片的管脚供电图如下。

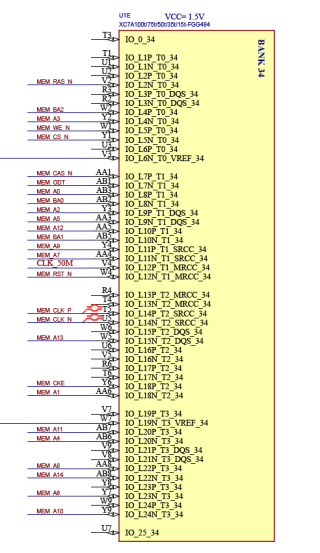

BANK34 的管脚是 1.5V

你可以将 1.2V 的管脚放在 BANK16上,2.5V 的管脚放在 BANK15上

按下图照葫芦画瓢, VCCO_15 接2.5V,VCCO_16接1.2V

本回答被题主选为最佳回答 , 对您是否有帮助呢?解决 无用评论 打赏 举报

本回答被题主选为最佳回答 , 对您是否有帮助呢?解决 无用评论 打赏 举报

悬赏问题

- ¥15 有了解d3和topogram.js库的吗?有偿请教

- ¥100 任意维数的K均值聚类

- ¥15 stamps做sbas-insar,时序沉降图怎么画

- ¥15 unity第一人称射击小游戏,有demo,在原脚本的基础上进行修改以达到要求

- ¥15 买了个传感器,根据商家发的代码和步骤使用但是代码报错了不会改,有没有人可以看看

- ¥15 关于#Java#的问题,如何解决?

- ¥15 加热介质是液体,换热器壳侧导热系数和总的导热系数怎么算

- ¥100 嵌入式系统基于PIC16F882和热敏电阻的数字温度计

- ¥15 cmd cl 0x000007b

- ¥20 BAPI_PR_CHANGE how to add account assignment information for service line