Altera官网的工程师:

你们好,我在用FPGA设计DFT的仿真时碰到quartus 编译资源不够的问题,想问问你们怎么解决这个问题。我的仿真软件是modelsim10.5SE,quartus版本是quartus13.1SP4,器件是EP4CE40F23I7问题具体如下:

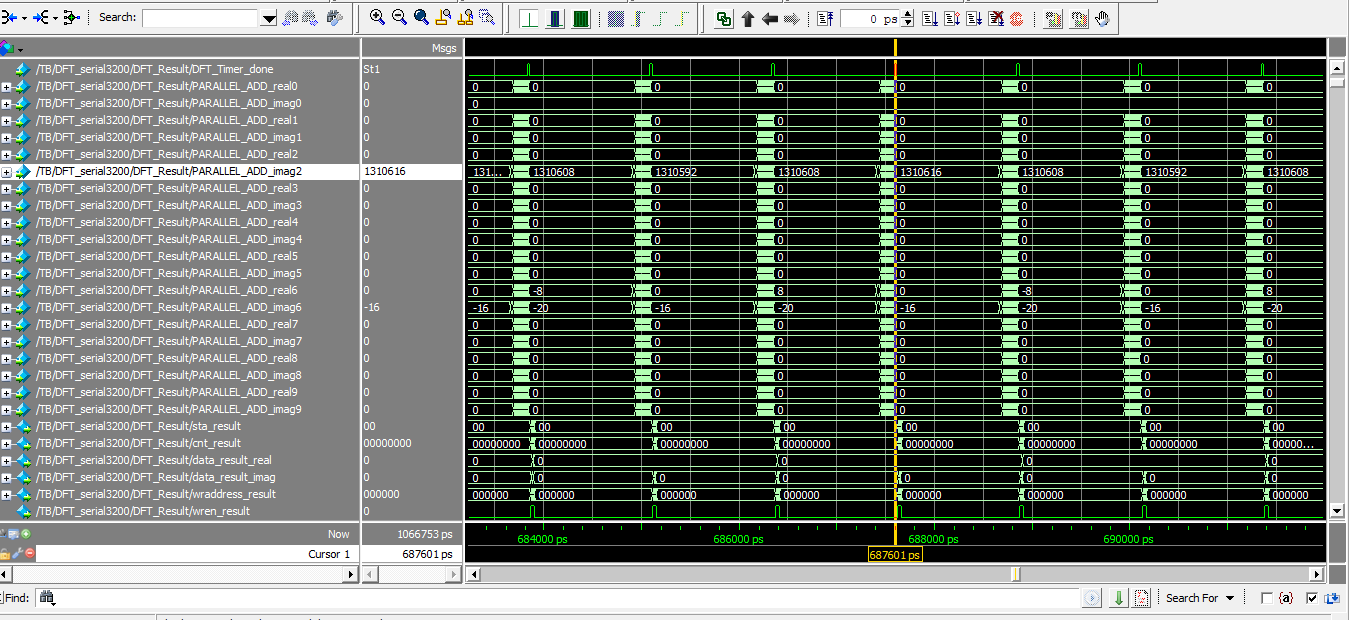

- 首先给出modelsim 仿真的结果图,

- Quartus编译结果 2.1 移植到quartus下进行编译,说明资源不够

参照官方文档,网址

https://www.intel.com/content/www/us/en/programmable/quartushelp/13.1/mergedProjects/hdl/vlog/vlog_file_dir_ram.htm

将(*ramstyle = "M-RAM"*) reg[15:0]data_mem [3200:0];将这个映射到RAM上,但编译结果还是这样的,

2.2屏蔽掉下图这个模块中的程序,

编译立马减少到

进入到SINCOS模块中,屏蔽掉

//(*ramstyle = "M-RAM"*) reg[15:0]data_mem [3200:0];

编译结果

定义不消耗资源。

写进去也不占用什么资源,同上的逻辑

但涉及到读表操作时,就会有这些问题,就会资源不够的问题

3 实验这几种写法编译得到的结果

(* ramstyle = "M512" ) reg[15:0]data_mem [`DFT_POINT-1:0];得到的结果,估计也不会太好,

( ramstyle = "M9K" *) reg[15:0]data_mem [3200-1:0];编译结果不好,

请教问题的核心,是怎么解决这个读取问题,降低读取资源,时间越快越好。

时间我统计了一下,这么计算80点的乘法加法运算,需要100M时钟100clk(1us)就可以实现,我程序中是算5个模块都编译不过去,我想算(50个模块*3相=150)模块逻辑,时间在15us 以内。怎么建立这个需求。

怎么读表省资源