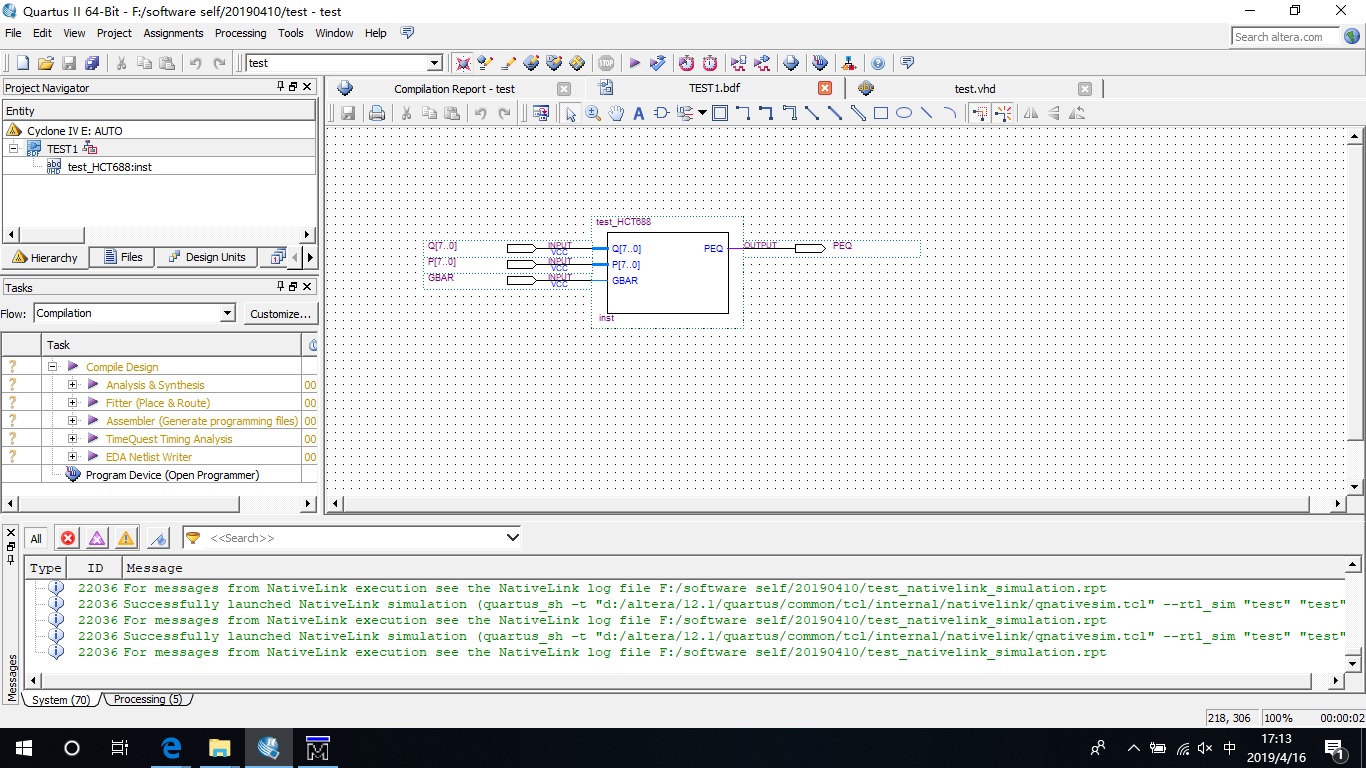

VHDL程序为

library IEEE;

use IEEE.Std_logic_1164.all;

entity test_HCT688 is

port(Q, P : in std_logic_vector(7 downto 0);

GBAR : in std_logic; PEQ : out std_logic);

end test_HCT688;

architecture VER1 of test_HCT688 is

begin

PEQ <= '0' when ((To_X01(P) = To_X01(Q)) and (GBAR = '0')) else '1';

end VER1;

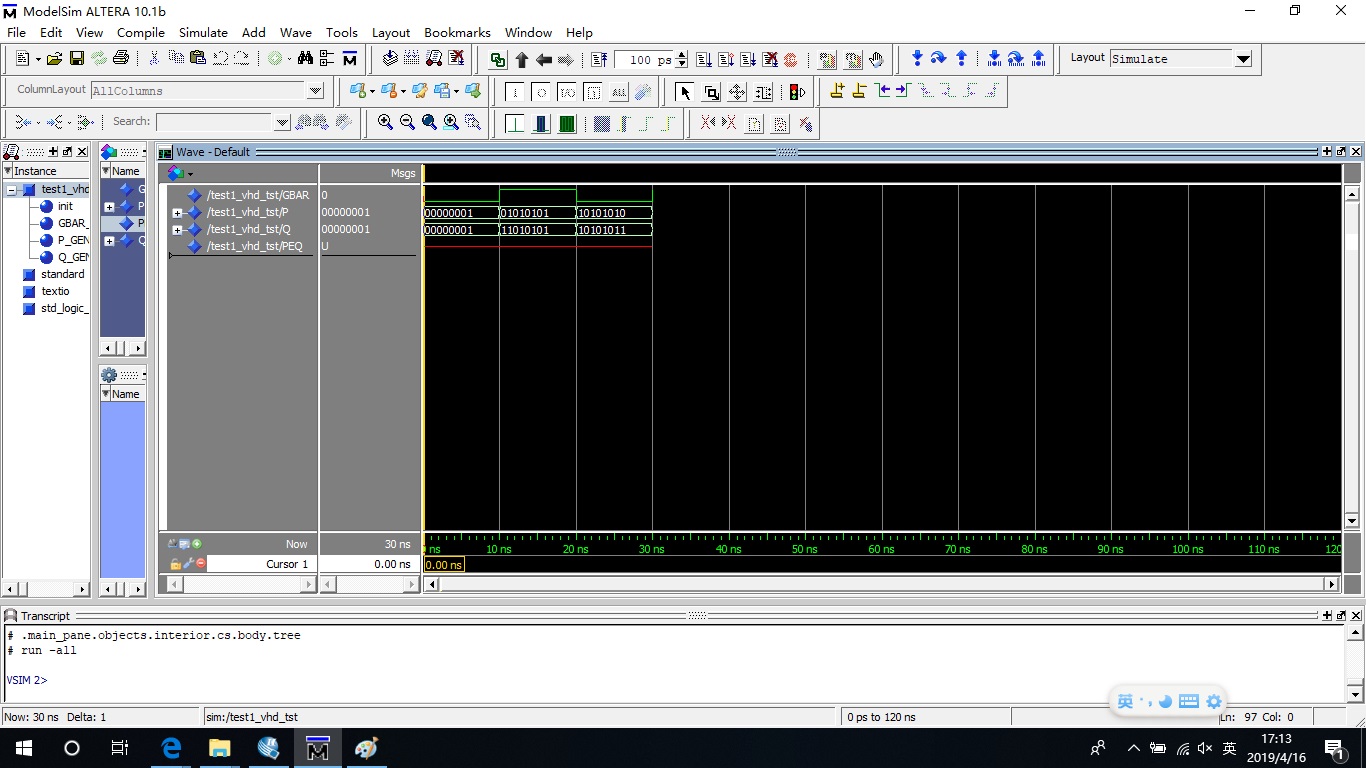

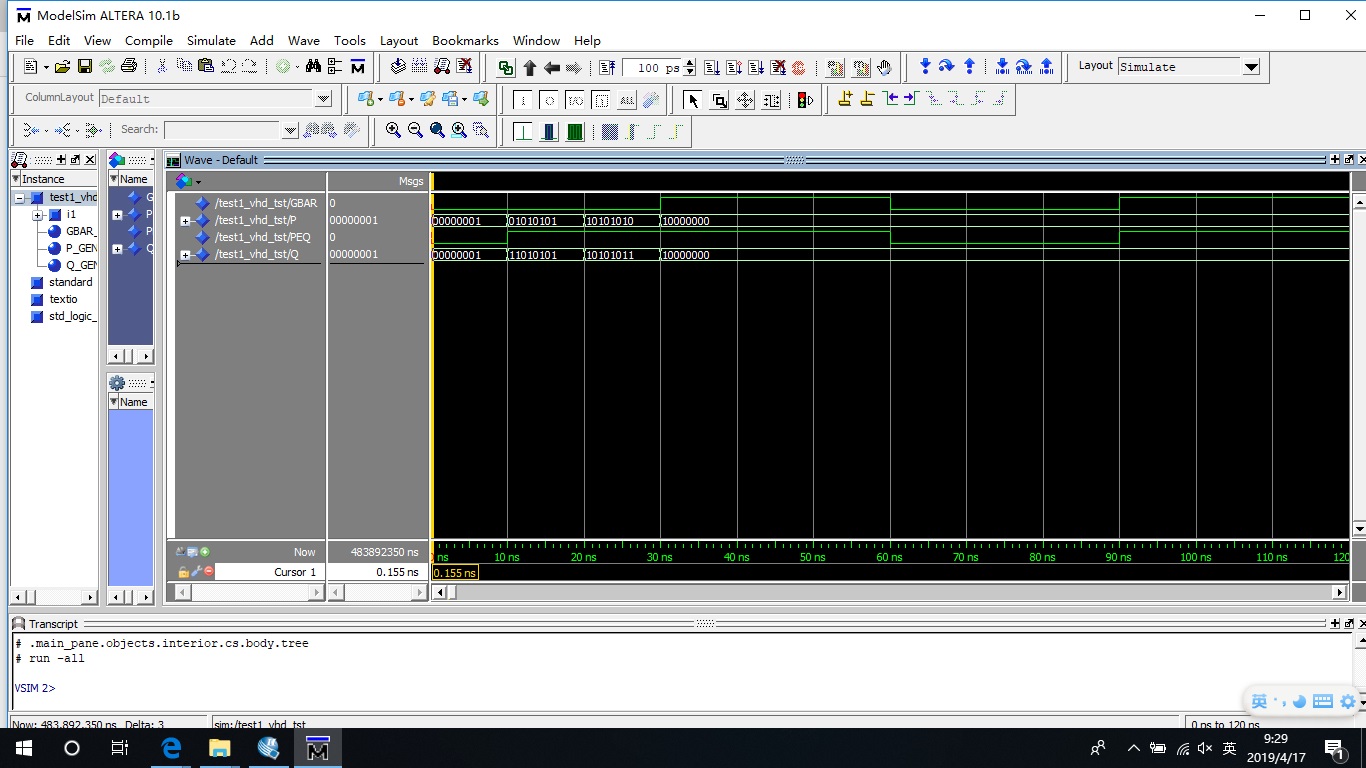

使用modelsim仿真无输出波形,testbench文件为: