module following_led(

input clk,

input rst,

output [3:0] led

);

reg [23 : 0] cnt_reg;

reg [ 3 : 0] light_reg;

always @ (posedge clk)

begin

if (rst)

cnt_reg <= 0;

else

cnt_reg <= + 1;

end

always @ (posedge clk)

begin

if (rst)

light_reg <= 4'b0001;

else if (cnt_reg == 24'hffffff) begin

if (light_reg == 4'b1000)

light_reg <= 4'b0001;

else

light_reg <= light_reg<< 1;

end

end

assign led = light_reg;

endmodule

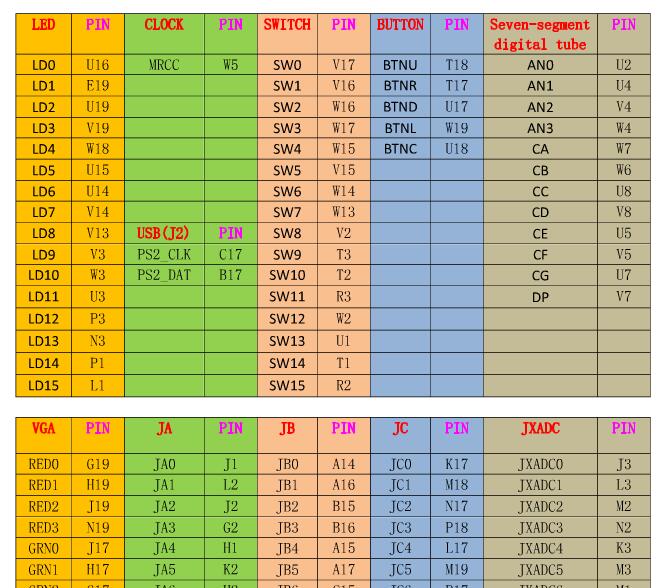

我用的是basys3。

在下面的verilog中rst应该分配什么引脚

- 写回答

- 好问题 0 提建议

- 关注问题

- 邀请回答

-

3条回答 默认 最新

East_Leegege 2017-10-29 06:51关注

East_Leegege 2017-10-29 06:51关注在按键有空余的情况下,用按键就可以,直接找一个空余按键对应管脚的名称链接起来就好了!

本回答被题主选为最佳回答 , 对您是否有帮助呢?解决 无用评论 打赏 举报