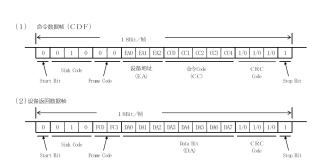

想用 FPGA芯片 EP1C3T144C8 做485通讯,如上图,数据帧18位,请教大师程序怎么做?

以下答案由GPT-3.5大模型与博主波罗歌共同编写:

要实现RS485通信功能,首先需要了解RS485协议和FPGA的串口通信技术。RS485是一种传输速率高、适用范围广的工业通信协议,支持多机通信和远距离传输等特点,适用于工业控制、汽车电子、安防监控等领域。而FPGA芯片是一种可编程芯片,能够实现各种数字逻辑功能和通信接口的设计。

以下是实现RS485通信的步骤:

定义RS485的通信参数:比特率、校验方式、停止位等等。根据通信参数,设置FPGA的串口通信模块,包括设置分频器、时钟信号、波特率等等。

定义数据帧格式:包括起始位、数据位、校验位和停止位。根据数据帧格式,设置FPGA芯片的状态机,实现数据帧的发送和接收功能。

实现发送/接收数据:将需要发送的数据放入FPGA芯片的FIFO缓冲区,然后按照RS485协议进行数据发送。接收数据时,先检测数据是否合法,然后将数据放入FIFO缓冲区。

编写测试程序,测试RS485通信功能是否正常。

下面是一个简单的FPGA实现RS485通信的代码示例。

module rs485 (

input clk,

input rst,

input [17:0] data_in,

output [17:0] data_out,

input tx_enable,

output reg tx_done,

input rx_enable,

output reg rx_done,

output reg dr);

reg [17:0] tx_data;

reg [2:0] tx_state;

reg [2:0] rx_state;

reg [17:0] rx_data;

wire rx = dr;

always @(posedge clk) begin

if (rst) begin

tx_data <= 18'h0000;

tx_state <= 3'h0;

rx_state <= 3'h0;

rx_data <= 18'h0000;

tx_done <= 1'b0;

rx_done <= 1'b0;

end else begin

case (tx_state)

3'h0: begin // idle

if (tx_enable) begin

tx_data <= data_in;

tx_state <= 3'h1;

tx_done <= 1'b0;

end

end

3'h1: begin // start bit

dr <= 1'b0;

tx_state <= 3'h2;

end

3'h2: begin // data bits

dr <= tx_data[0];

tx_data <= {tx_data[16:1], 1'b0};

if (tx_data == 18'h0000) begin

tx_state <= 3'h3;

end

end

3'h3: begin // stop bit

dr <= 1'b1;

tx_state <= 3'h0;

tx_done <= 1'b1;

end

endcase

case (rx_state)

3'h0: begin // idle

if (rx) begin

rx_data <= 18'h0000;

rx_state <= 3'h1;

rx_done <= 1'b0;

end

end

3'h1: begin // start bit

if (!rx) begin

rx_state <= 3'h2;

end

end

3'h2: begin // data bits

rx_data <= {rx_data[16:1], rx};

if (rx_data == 18'h0000) begin

rx_state <= 3'h3;

end

end

3'h3: begin // stop bit

rx_state <= 3'h0;

rx_done <= 1'b1;

end

endcase

end

end

assign data_out = rx_data;

endmodule

这个代码实现了一个简单的RS485通信模块,包括数据发送和接收功能,可以通过修改参数来适配不同的通信需求。

如果我的回答解决了您的问题,请采纳!